2020年10月1日

Zephyr OSで遊ぼう その15 - SMP対応の準備、コンテキストスイッチの実装、中編2、既存実装調査

目次: Zephyr

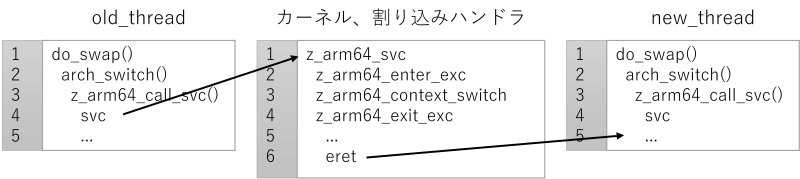

前回は、新しいコンテキストスイッチ関数に対応しているAArch64の実装のうち、共通部分からアーキテクチャ依存部分に至るまでを調べました。引き続きアーキテクチャ依存部分を調べます。

アーキ依存部分の処理(AArch64)

コンテキストスイッチのアーキテクチャ依存部分(AArch64向けarch_switch())の実装はほぼ全てアセンブラで実装されています。

コンテキストスイッチの本体はz_arm64_context_switchです。x0がnew_thread, x1がold_threadだと思って動きます。コンテキストスイッチの仕事はレジスタの値を切り替え前のスレッド構造体(old_thread)に退避し、切り替え後のスレッド構造体(new_thread)からレジスタの値を復旧させることです。

AArch64の新しい形式のコンテキストスイッチarch_switch() 実装

// zephyr/arch/arm/core/aarch64/switch.S

GTEXT(z_arm64_svc)

SECTION_FUNC(TEXT, z_arm64_svc)

z_arm64_enter_exc x2, x3, x4 /* ★レジスタをスタックに退避(切り替え前のスレッド)★ */

switch_el x1, 3f, 2f, 1f

3:

mrs x0, esr_el3

b 0f

2:

mrs x0, esr_el2

b 0f

1:

mrs x0, esr_el1

0:

lsr x1, x0, #26

cmp x1, #0x15 /* 0x15 = SVC */

bne inv

/* Demux the SVC call */

and x1, x0, #0xff

cmp x1, #_SVC_CALL_CONTEXT_SWITCH

beq context_switch /* ★以下参照★ */

...

context_switch:

/*

* Retrieve x0 and x1 from the stack:

* - x0 = new_thread->switch_handle = switch_to thread

* - x1 = x1 = &old_thread->switch_handle = current thread

*/

ldp x0, x1, [sp, #(16 * 10)] /* ★x1 = 切り替え前、x0 = 切り替え後のスレッド★ */

/* Get old thread from x1 */

sub x1, x1, ___thread_t_switch_handle_OFFSET

/* Switch thread */

bl z_arm64_context_switch /* ★コンテキストスイッチ本体(スタックが切り替わる)★ */

exit:

z_arm64_exit_exc x0, x1, x2 /* ★レジスタをスタックから復旧(切り替え後のスレッド)★ */

...

/**

* @brief Routine to handle context switches

*

* This function is directly called either by _isr_wrapper() in case of

* preemption, or z_arm64_svc() in case of cooperative switching.

*/

GTEXT(z_arm64_context_switch)

SECTION_FUNC(TEXT, z_arm64_context_switch)

/* addr of callee-saved regs in thread in x2 */

ldr x2, =_thread_offset_to_callee_saved

add x2, x2, x1

/* Store rest of process context including x30 */

stp x19, x20, [x2], #16

stp x21, x22, [x2], #16

stp x23, x24, [x2], #16

stp x25, x26, [x2], #16

stp x27, x28, [x2], #16

stp x29, x30, [x2], #16

/* Save the current SP */

mov x1, sp

str x1, [x2]

/* addr of callee-saved regs in thread in x2 */

ldr x2, =_thread_offset_to_callee_saved

add x2, x2, x0

/* Restore x19-x29 plus x30 */

ldp x19, x20, [x2], #16

ldp x21, x22, [x2], #16

ldp x23, x24, [x2], #16

ldp x25, x26, [x2], #16

ldp x27, x28, [x2], #16

ldp x29, x30, [x2], #16

ldr x1, [x2]

mov sp, x1 /* ★ここで切り替え後のスレッドのスタックに変わる★ */

#ifdef CONFIG_TRACING

stp xzr, x30, [sp, #-16]!

bl sys_trace_thread_switched_in

ldp xzr, x30, [sp], #16

#endif

/* We restored x30 from the process stack. There are three possible

* cases:

*

* - We return to z_arm64_svc() when swapping in a thread that was

* swapped out by z_arm64_svc() before jumping into

* z_arm64_exit_exc()

* - We return to _isr_wrapper() when swapping in a thread that was

* swapped out by _isr_wrapper() before jumping into

* z_arm64_exit_exc()

* - We return (jump) into z_thread_entry_wrapper() for new threads

* (see thread.c)

*/

ret

// zephyr/include/arm/aarch64/thread.h

struct _callee_saved {

uint64_t x19;

uint64_t x20;

uint64_t x21;

uint64_t x22;

uint64_t x23;

uint64_t x24;

uint64_t x25;

uint64_t x26;

uint64_t x27;

uint64_t x28;

uint64_t x29; /* FP */

uint64_t x30; /* LR */

uint64_t sp;

};

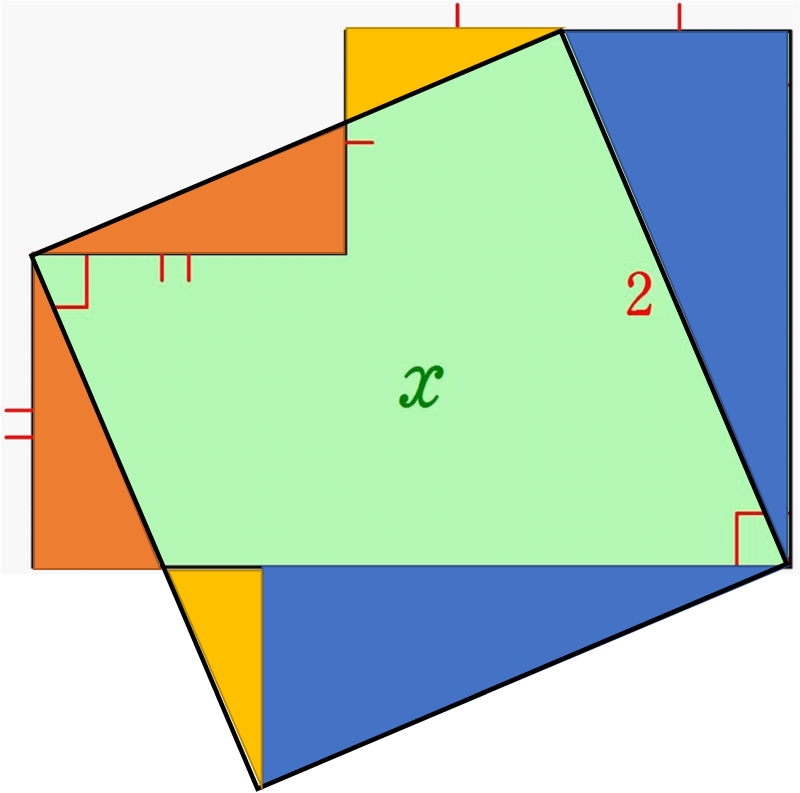

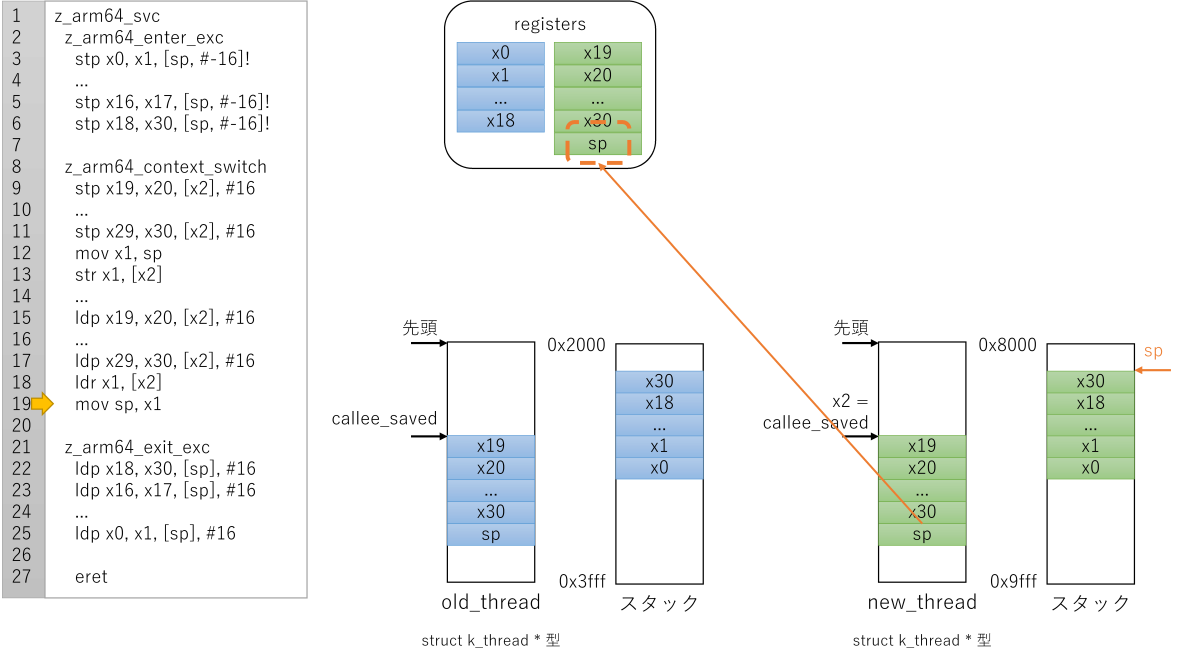

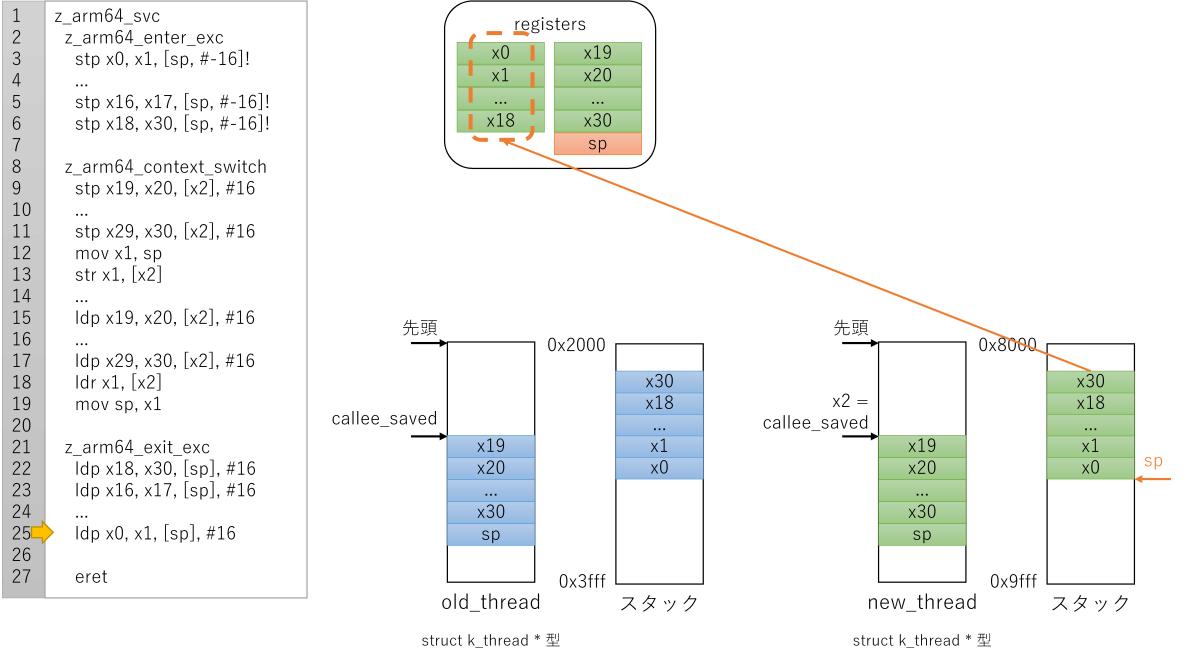

コードを見て一発で理解するのは厳しいので、処理の概要を書いておきます。

コンテキストスイッチの際にスタックが切り替わります。z_arm64_exit_exc x0, x1, x2はシステムコールを呼んだスレッド(=切り替え前のスレッド)ではなく、コンテキストスイッチ後のスレッドのスタックからレジスタを復旧します。

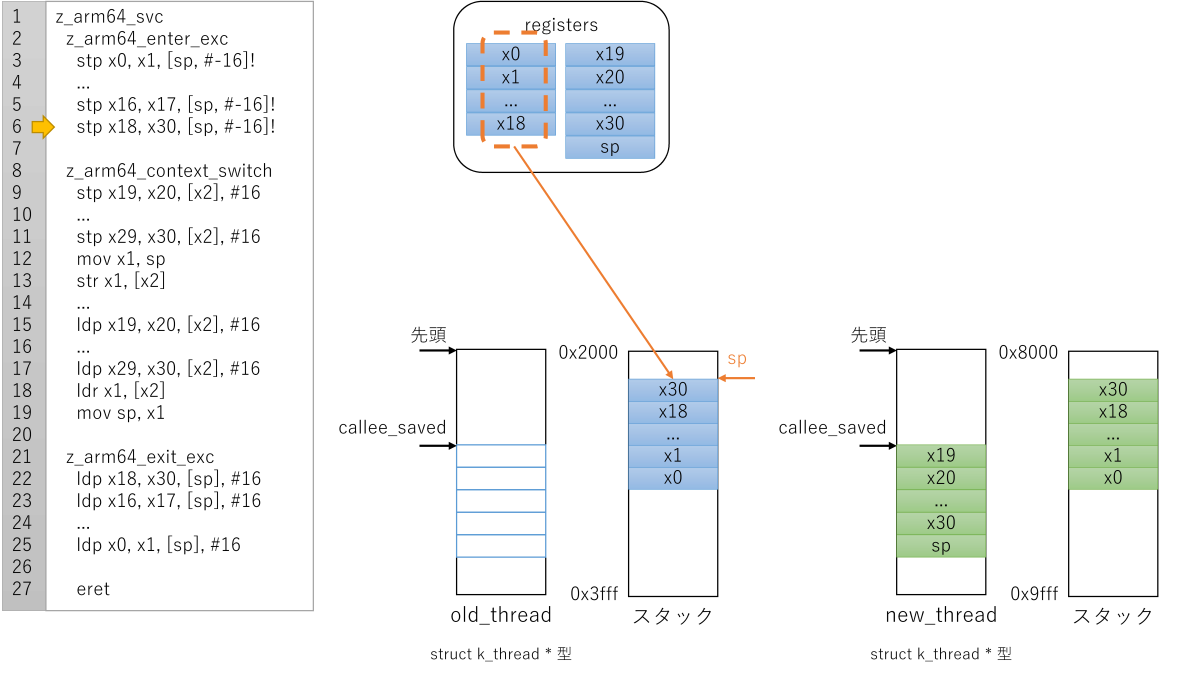

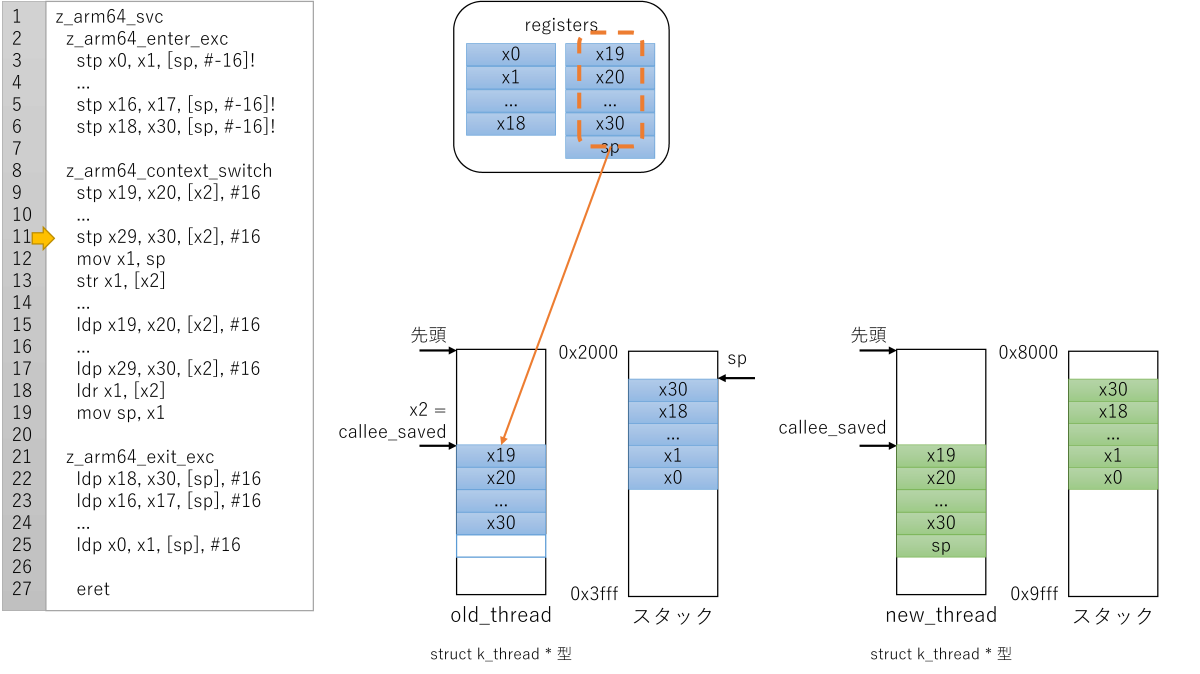

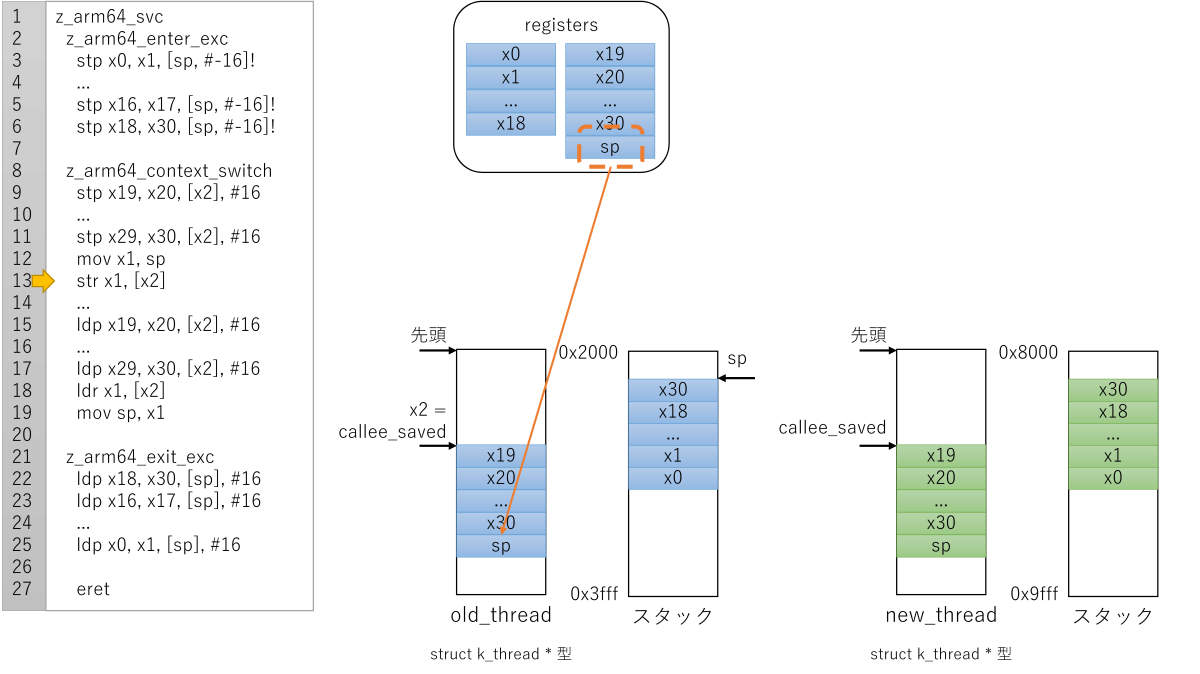

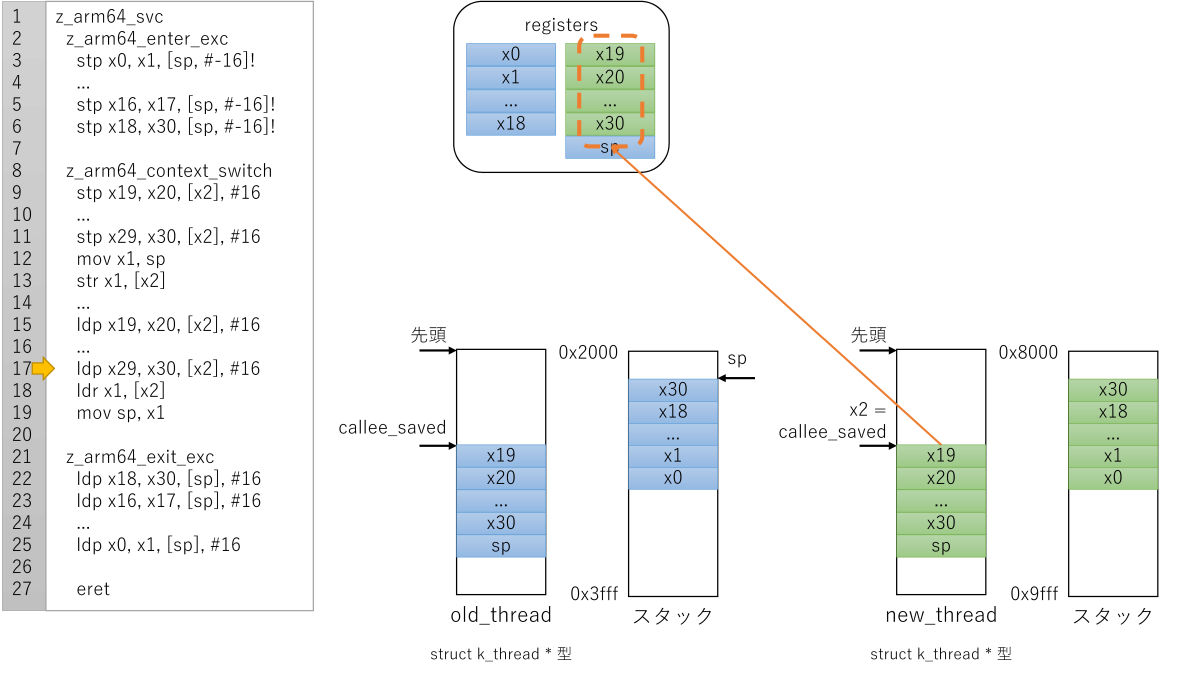

これも文章だと何だかわからないので、紙芝居を書いておきます。

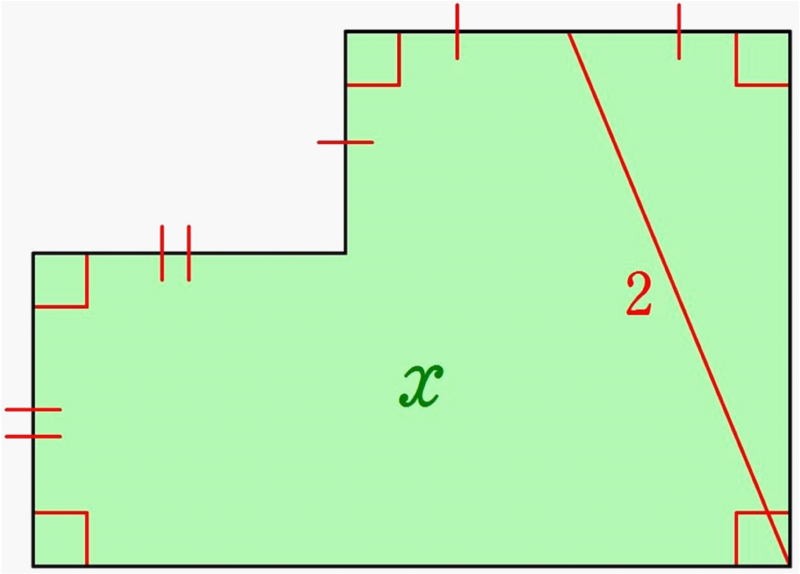

Zephyr AArch64のコンテキストスイッチ: 例外ハンドラ先頭

Zephyr AArch64のコンテキストスイッチ: 例外ハンドラ入り口、スタックへレジスタ退避

Zephyr AArch64のコンテキストスイッチ: コンテキストスイッチ前半、切り替え前スレッド構造体へレジスタ退避

Zephyr AArch64のコンテキストスイッチ: コンテキストスイッチ前半、切り替え前スレッド構造体へスタックポインタ退避

Zephyr AArch64のコンテキストスイッチ: コンテキストスイッチ後半、切り替え後スレッド構造体からレジスタ復旧

Zephyr AArch64のコンテキストスイッチ: コンテキストスイッチ後半、切り替え後スレッド構造体からスタックポインタ復旧(=スタック切り替え)

Zephyr AArch64のコンテキストスイッチ: 例外ハンドラ入り口、切り替え後のスタックからレジスタ復旧

図には書きませんでしたが、例外からリターンする命令(eret命令)が参照するレジスタ(SPSR, ELRレジスタ)もスタックに退避、復旧しています。従ってeretが戻る先は切り替え後のスレッドのコードです。

コメント一覧

- コメントはありません。

この記事にコメントする

この記事にコメントする

2020年10月3日

Zephyr OSで遊ぼう その16 - SMP対応の準備、コンテキストスイッチの実装、後編1、RISC-Vのコンテキストスイッチ

目次: Zephyr

前回は、AArch64の実装を調べました。いよいよ新しい方式のコンテキストスイッチを実装したいところですが、その前にもう一つだけRISC-Vの既存実装を調べます。

RISC-Vの2つのコンテキストスイッチ経路

RISC-V向け実装において、コンテキストスイッチが行われる条件は2つあります。1つはスリープしたときなどに呼ばれる明示的なコンテキストスイッチです。do_swap() を経由します。もう1つは割り込み発生時に行われるプリエンプションです。

- 明示的コンテキストスイッチ

- do_swap() -> arch_switch() ラッパー関数 -> z_riscv_switch() -> ecall -> __irq_wrapper -> is_syscall -> reschedule -> no_reschedule -> mret

- プリエンプション

- (任意の場所) -> __irq_wrapper -> is_interrupt -> on_irq_stack -> 割り込みハンドラ(isr_timer() など) -> on_thread_stack -> reschedule -> no_reschedule -> mret

明示的コンテキストスイッチについては、以前(2020年9月29日の日記参照)実装したラッパー関数がスタート地点となります。コードを変更する前に、従来のコンテキストスイッチがどんな経路を通るか確認します。

arch_switch() ラッパー関数 -> z_riscv_switch() -> ecall -> __irq_wrapper -> is_syscall

// zephyr/arch/riscv/include/kernel_arch_func.h

static inline void arch_switch(void *switch_to, void **switched_from)

{

z_riscv_switch(switch_to, switched_from);

}

// zephyr/arch/riscv/core/swap.S

/*

* void z_riscv_switch(void *switch_to, void **switched_from)

*/

SECTION_FUNC(exception.other, z_riscv_switch)

/* Make a system call to perform context switch */

ecall //★例外を発生させる★

jalr x0, ra

// zephyr/arch/riscv/core/isr.S

/*

* Handler called upon each exception/interrupt/fault

* In this architecture, system call (ECALL) is used to perform context

* switching or IRQ offloading (when enabled).

*/

SECTION_FUNC(exception.entry, __irq_wrapper)

/* Allocate space on thread stack to save registers */

addi sp, sp, -__z_arch_esf_t_SIZEOF

...

/*

* Check if exception is the result of an interrupt or not.

* (SOC dependent). Following the RISC-V architecture spec, the MSB

* of the mcause register is used to indicate whether an exception

* is the result of an interrupt or an exception/fault. But for some

* SOCs (like pulpino or riscv-qemu), the MSB is never set to indicate

* interrupt. Hence, check for interrupt/exception via the __soc_is_irq

* function (that needs to be implemented by each SOC). The result is

* returned via register a0 (1: interrupt, 0 exception)

*/

jal ra, __soc_is_irq

/* If a0 != 0, jump to is_interrupt */

addi t1, x0, 0

bnez a0, is_interrupt //★割り込みの場合はこちらにジャンプする★

/*

* If the exception is the result of an ECALL, check whether to

* perform a context-switch or an IRQ offload. Otherwise call _Fault

* to report the exception.

*/

csrr t0, mcause

li t2, SOC_MCAUSE_EXP_MASK

and t0, t0, t2

li t1, SOC_MCAUSE_ECALL_EXP

/*

* If mcause == SOC_MCAUSE_ECALL_EXP, handle system call,

* otherwise handle fault

*/

beq t0, t1, is_syscall //★ecallの場合はこちらにジャンプする★

/*

* Call _Fault to handle exception.

* Stack pointer is pointing to a z_arch_esf_t structure, pass it

* to _Fault (via register a0).

* If _Fault shall return, set return address to no_reschedule

* to restore stack.

*/

addi a0, sp, 0

la ra, no_reschedule

tail _Fault //★いずれでもなければ停止させる★

...

Zephyr RISC-V向け実装では、割り込み・例外ハンドラは1つだけです。割り込みも例外も全て __irq_wrapperに飛んできますから、最初の方で要因をチェックして仕分けしています。RISC-Vの規格としては割り込み要因ごとに別の割り込みハンドラに飛べる形式(ベクタ形式)もありますが、Zephyrは使っていません。

明示的コンテキストスイッチの実行経路: is_syscall -> reschedule -> no_reschedule -> mret

// zephyr/arch/riscv/core/isr.S

is_syscall:

/*

* A syscall is the result of an ecall instruction, in which case the

* MEPC will contain the address of the ecall instruction.

* Increment saved MEPC by 4 to prevent triggering the same ecall

* again upon exiting the ISR.

*

* It's safe to always increment by 4, even with compressed

* instructions, because the ecall instruction is always 4 bytes.

*/

RV_OP_LOADREG t0, __z_arch_esf_t_mepc_OFFSET(sp)

addi t0, t0, 4

RV_OP_STOREREG t0, __z_arch_esf_t_mepc_OFFSET(sp)

...

/*

* Go to reschedule to handle context-switch

*/

j reschedule //★コンテキストスイッチ★

...

reschedule:

...

/* Get reference to _kernel */

la t0, _kernel

/* Get pointer to _kernel.current */

RV_OP_LOADREG t1, _kernel_offset_to_current(t0)

/*

* Save callee-saved registers of current thread

* prior to handle context-switching

*/

RV_OP_STOREREG s0, _thread_offset_to_s0(t1)

RV_OP_STOREREG s1, _thread_offset_to_s1(t1)

...

RV_OP_STOREREG s10, _thread_offset_to_s10(t1)

RV_OP_STOREREG s11, _thread_offset_to_s11(t1)

...

/*

* Save stack pointer of current thread and set the default return value

* of z_swap to _k_neg_eagain for the thread.

*/

RV_OP_STOREREG sp, _thread_offset_to_sp(t1)

la t2, _k_neg_eagain

lw t3, 0x00(t2)

sw t3, _thread_offset_to_swap_return_value(t1)

/* Get next thread to schedule. */

RV_OP_LOADREG t1, _kernel_offset_to_ready_q_cache(t0)

/*

* Set _kernel.current to new thread loaded in t1

*/

RV_OP_STOREREG t1, _kernel_offset_to_current(t0)

/* Switch to new thread stack */

RV_OP_LOADREG sp, _thread_offset_to_sp(t1)

/* Restore callee-saved registers of new thread */

RV_OP_LOADREG s0, _thread_offset_to_s0(t1)

RV_OP_LOADREG s1, _thread_offset_to_s1(t1)

...

RV_OP_LOADREG s10, _thread_offset_to_s10(t1)

RV_OP_LOADREG s11, _thread_offset_to_s11(t1)

...

no_reschedule:

...

/* Restore MEPC register */

RV_OP_LOADREG t0, __z_arch_esf_t_mepc_OFFSET(sp)

csrw mepc, t0

/* Restore SOC-specific MSTATUS register */

RV_OP_LOADREG t0, __z_arch_esf_t_mstatus_OFFSET(sp)

csrw mstatus, t0

...

/* Restore caller-saved registers from thread stack */

RV_OP_LOADREG ra, __z_arch_esf_t_ra_OFFSET(sp)

RV_OP_LOADREG gp, __z_arch_esf_t_gp_OFFSET(sp)

RV_OP_LOADREG tp, __z_arch_esf_t_tp_OFFSET(sp)

RV_OP_LOADREG t0, __z_arch_esf_t_t0_OFFSET(sp)

...

RV_OP_LOADREG a6, __z_arch_esf_t_a6_OFFSET(sp)

RV_OP_LOADREG a7, __z_arch_esf_t_a7_OFFSET(sp)

/* Release stack space */

addi sp, sp, __z_arch_esf_t_SIZEOF

/* Call SOC_ERET to exit ISR */

SOC_ERET

コメントが丁寧に書いてあって素晴らしいですね。コンテキストスイッチの手順はAArch64の実装とほぼ同じですが、AAarch64は明示的なコンテキストスイッチとプリエンプションが独立して実装されており、RISC-Vはrescheduleで両者が合流する点が違います。コンテキストスイッチの説明は先日(2020年10月1日の日記参照)の紙芝居が参考になるかと思います。

明示的なコンテキストスイッチとプリエンプションの部分が大体仕分けできました。いよいよ実装に挑みます。続きはまた。

コメント一覧

- コメントはありません。

この記事にコメントする

この記事にコメントする

2020年10月4日

Zephyr OSで遊ぼう その17 - SMP対応の準備、コンテキストスイッチの実装、後編2、明示的コンテキストスイッチ

目次: Zephyr

前回はRISC-Vの明示的なコンテキストスイッチの既存実装を調べました。今回は新しいコンテキストスイッチを実装します。

対応方針

従来と新形式のコンテキストスイッチで大きく異なるのは、下記の要素です。

| 明示的コンテキストスイッチ | 従来 | 新形式 |

|---|---|---|

| 割り込まれた処理の返り値 | 設定必要(thread->arch.swap_return_value) | 設定不要(do_swap() がやってくれる) |

| 切り替え元スレッド | _kernel.cpu[0].current | a1レジスタ(引数old_thread->switch_handle) |

| 切り替え先スレッド | _kernel.ready_q.cache | a0レジスタ(引数new_thread->switch_handle) |

| プリエンプション | 従来 | 新形式 |

|---|---|---|

| 割り込まれた処理の返り値 | 設定必要(thread->arch.swap_return_value) | 設定不要(do_swap() がやってくれる) |

| 切り替え元スレッド | _kernel.cpu[0].current | _kernel.cpu[n].current(※) |

| 切り替え先スレッド | _kernel.ready_q.cache | z_get_next_switch_handle() の返り値 |

(※)初めは切り替え元スレッドですが、z_get_next_switch_handle() を呼ぶと、切り替え先のスレッドに変わります。

割り込まれた処理の返り値

割り込まれた処理の返り値を -EINTRに設定するために必要な処理は、do_swap() がやるため実装は必要ありません。従来の処理が間違って発動しないように #ifdefで消しておきます。

swap_return_valueは不要

// zephyr/arch/riscv/core/isr.Sの差分

+ /* Save stack pointer of current thread. */

+ RV_OP_STOREREG sp, _thread_offset_to_sp(t1) //★スタックポインタ保存は新しい形式でも必要★

+

+#ifndef CONFIG_USE_SWITCH

/*

- * Save stack pointer of current thread and set the default return value

- * of z_swap to _k_neg_eagain for the thread.

+ * Set the default return value of z_swap to _k_neg_eagain for

+ * the thread.

*/

- RV_OP_STOREREG sp, _thread_offset_to_sp(t1)

la t2, _k_neg_eagain

lw t3, 0x00(t2)

sw t3, _thread_offset_to_swap_return_value(t1) //★返り値設定は不要★

+#endif /* !CONFIG_USE_SWITCH */

// zephyr/arch/riscv/core/offsets/offsets.c

//★_thread_offset_to_swap_return_value() マクロを使えるようにする仕掛け★

#ifndef CONFIG_USE_SWITCH

GEN_OFFSET_SYM(_thread_arch_t, swap_return_value); //★いらない★

#endif /* !CONFIG_USE_SWITCH */

// zephyr/include/arch/riscv/thread.h

struct _thread_arch {

#ifndef CONFIG_USE_SWITCH

uint32_t swap_return_value; /* Return value of z_swap() */ //★いらない★

#endif /* !CONFIG_USE_SWITCH */

};

処理を消すだけでも動きますが、swap_return_valueを間違って使うとバグの元なので、変数宣言ごと消します。

切り替え元/切り替え先スレッド

従来は常に _kernel変数を見れば良かったので楽でした。新形式では明示的コンテキストスイッチとプリエンプションで切り替え元/切り替え先スレッドの取得方法が異なります。よって、明示的コンテキストスイッチとプリエンプションで、スレッドの扱いを揃える必要があります。

設計する人の自由で決めて構いませんが、今回は合流地点(reschedule)に辿り着く前に切り替え元(old_thread)、切り替え先スレッド(new_thread)を取得し _currentにnew_threadを設定し, t1レジスタにold_threadを設定することとします。

明示的コンテキストスイッチの場合、切り替え元と切り替え先スレッドは引数で渡されます。引数はハンドラの先頭でスタックに保存されますので、スタックからロードできます。

切り替え元/切り替え先スレッドの取得

// zephyr/arc/riscv/core/isr.S

#ifdef CONFIG_USE_SWITCH

/*

* Get new_thread and old_thread from stack.

* - a0 = new_thread->switch_handle -> _current

* - a1 = &old_thread->switch_handle -> t1

*/

/* Get reference to _kernel */

la t2, _kernel

/* Get new_thread from stack */

RV_OP_LOADREG t1, __z_arch_esf_t_a0_OFFSET(sp) //★スタックから切り替え先スレッド取得★

/* Set new thread to _current */

RV_OP_STOREREG t1, ___cpu_t_current_OFFSET(t2) //★(2) この関数内でnew_threadを _currentに設定★

/* Get old_thread from stack and set it to t1 */

RV_OP_LOADREG t1, __z_arch_esf_t_a1_OFFSET(sp) //★(1)スタックから切り替え元スレッド取得、t1レジスタにold_threadを設定★

addi t1, t1, -___thread_t_switch_handle_OFFSET //★(A) old_thread->switch_handleの更新★

#endif

/*

* Go to reschedule to handle context-switch

*/

j reschedule

// zephyr/arch/riscv/core/thread.c

void arch_new_thread(struct k_thread *thread, k_thread_stack_t *stack,

char *stack_ptr, k_thread_entry_t entry,

void *p1, void *p2, void *p3)

{

struct __esf *stack_init;

...

#ifdef CONFIG_USE_SWITCH

thread->switch_handle = thread; //★(B) switch_handleの初期値設定★

#endif

}

処理 (1) でnew_threadを _currentに設定していて、処理 (2) でold_threadをt1レジスタに設定してから、rescheduleにジャンプします。

wait_for_switch() への対処

スレッドと直接関係ないもののold_thread->switch_handleを更新する処理も重要です。あとでハマりやすいポイントですので、補足しておきます。

以前、少し言及しましたが(2020年9月30日の日記参照)、switch_handleの更新を実装し忘れるとCONFIG_SMPを有効にしたときにwait_for_switch() で無限ループに陥ってハマります。

Zephyrのドキュメントにてarch_switch() を見ると(Zephyr Project: arch_switch)、スレッドにレジスタを退避後、old_thread->switch_handleをNULL以外の値で書き換える必要があります。これはコンテキストスイッチ処理内で行う (A) の処理に相当します。

実はこれだけではダメです。wait_for_switch() はコンテキストスイッチの「前」に呼ばれるからです。一番最初に発生するコンテキストスイッチのold_thread->switch_handleは誰も書き換えてくれないのでハングします。この問題の対処としてスレッド生成時にswitch_handleを初期化する (B) の処理を実装しています。

次回はプリエンプションの実装をします。

コメント一覧

- コメントはありません。

この記事にコメントする

この記事にコメントする

2020年10月5日

Zephyr OSで遊ぼう その18 - SMP対応の準備、コンテキストスイッチの実装、後編3、プリエンプション

目次: Zephyr

前回はRISC-Vの2つあるコンテキストスイッチのうち、明示的なコンテキストスイッチを実装しました。今回はもう一方のプリエンプションを実装します。

対応方針(再掲)

従来と新形式のコンテキストスイッチで大きく異なるのは、下記の要素です。

| 明示的コンテキストスイッチ | 従来 | 新形式 |

|---|---|---|

| 割り込まれた処理の返り値 | 設定必要(thread->arch.swap_return_value) | 設定不要(do_swap() がやってくれる) |

| 切り替え元スレッド | _kernel.cpu[0].current | a1レジスタ(引数old_thread->switch_handle) |

| 切り替え先スレッド | _kernel.ready_q.cache | a0レジスタ(引数new_thread->switch_handle) |

| プリエンプション | 従来 | 新形式 |

|---|---|---|

| 割り込まれた処理の返り値 | 設定必要(thread->arch.swap_return_value) | 設定不要(do_swap() がやってくれる) |

| 切り替え元スレッド | _kernel.cpu[0].current | _kernel.cpu[n].current(※) |

| 切り替え先スレッド | _kernel.ready_q.cache | z_get_next_switch_handle() の返り値 |

(※)初めは切り替え元スレッドですが、z_get_next_switch_handle() を呼ぶと、切り替え先のスレッドに変わります。

割り込まれた処理の返り値

明示的プリエンプションと共通の部分のため、改めて直す必要はないです。

切り替え元/切り替え先スレッド

かなり処理が変わるため、#ifdefだとごちゃごちゃしてしまいます。スレッド取得の専用マクロを作ります。

切り替え元、切り替え先スレッドの取得

// zephyr/arch/riscv/core/isr.S

/*

* xcpu: pointer of _kernel.cpus[n]

* xold: (result) old thread

* xnew: (result) next thread to schedule

*

* after this function a0 is broken

*/

.macro z_riscv_get_next_switch_handle xcpu, xold, xnew

#ifdef CONFIG_USE_SWITCH

addi sp, sp, -RV_REGSIZE*2 //★新たな処理★

RV_OP_STOREREG ra, RV_REGSIZE(sp)

addi a0, sp, 0 //★スタックの先頭へのポインタを第一引数old_threadとする★

jal ra, z_arch_get_next_switch_handle //★(2) この関数内で _currentがnew_threadに設定される★

addi xnew, a0, 0 //★a0が返り値、切り替え先のスレッドが入っている★

RV_OP_LOADREG xold, 0(sp) //★スタック先頭に切り替え元のスレッドが入っている★

RV_OP_LOADREG ra, RV_REGSIZE(sp)

addi sp, sp, RV_REGSIZE*2

#else

/* Get pointer to _kernel.current */ //★従来処理★

RV_OP_LOADREG xold, _kernel_offset_to_current(xcpu) //★切り替え元スレッド★

RV_OP_LOADREG xnew, _kernel_offset_to_ready_q_cache(xcpu) //★切り替え先スレッド★

#endif

.endm

// zephyr/arch/riscv/core/thread.c

#ifdef CONFIG_USE_SWITCH

void *z_arch_get_next_switch_handle(struct k_thread **old_thread)

{

*old_thread = _current; //★スタックの先頭に現在のスレッド(= 切り替え元のスレッド)を保存★

return z_get_next_switch_handle(*old_thread);

}

#endif

わざわざスタックのポインタを経由して書き込むなんてややこしいことをせず、RV_OP_LOADREG xold, _kernel_offset_to_current(xcpu) で良いのでは?と思うかもしれませんが、z_arch_get_next_switch_handle() の呼び出しでどのレジスタが壊れるかわかりませんから、結局 xoldをスタックに退避する必要があります。

明示的コンテキストスイッチと処理を共有しているため、ちょっとわかりにくいですが、プリエンプションの中心となる処理はこの辺りです。

プリエンプション処理の差分

// zephyr/arch/riscv/core/isr.S

#ifdef CONFIG_PREEMPT_ENABLED

- /*

- * Check if we need to perform a reschedule

- */

-

- /* Get pointer to _kernel.current */

- RV_OP_LOADREG t2, _kernel_offset_to_current(t1)

-

/*

* Check if next thread to schedule is current thread.

* If yes do not perform a reschedule

*/

- RV_OP_LOADREG t3, _kernel_offset_to_ready_q_cache(t1)

+ z_riscv_get_next_switch_handle t1, t2, t3

beq t3, t2, no_reschedule

+

+#ifdef CONFIG_USE_SWITCH

+ /* Set old thread to t1 */

+ addi t1, t2, 0 //★(1) t1レジスタにold_threadを設定する★

+#endif

+

前回決めたとおり、合流地点(reschedule)に辿り着く前に切り替え元(old_thread)、切り替え先スレッド(new_thread)を取得し _currentにnew_threadを設定し, t1レジスタにold_threadを設定します。

処理 (1) でnew_threadを _currentに設定していて、処理 (2) でold_threadをt1レジスタに設定してから、rescheduleに到達します。プリエンプション処理のすぐ後にrescheduleラベルがあるので、ジャンプは不要です。

とても長くなってしまいましたが、新しい形式のコンテキストスイッチを実装できました。苦労の割に動作の見た目は何も変わりませんが、本命のSMP対応に活用するためなので我慢です。

コメント一覧

- コメントはありません。

この記事にコメントする

この記事にコメントする

2020年10月10日

Zephyr OSで遊ぼう その19 - SMP対応CPUコア数1、ビルドエラーの対処1

目次: Zephyr

新しい形式のコンテキストスイッチを実装しました。以前書いたとおり、SMP対応は下記の手順で進めています。再掲しておきましょう。

- SMPの前提条件、新しいコンテキストスイッチ方式に対応する(CONFIG_USE_SWITCH, CONFIG_USE_SWITCH_SUPPORTED)

- (今ここ)SMPに対応する(CONFIG_SMP)、ただしCPUコア数は1

- 先頭ではないコア(mhartid != 0)で動作させる、ただしCPUコア数は1

- CPUコア数を1以上にする(CONFIG_SMP)

やっと最初の項目が終わったところです。いよいよCONFIG_SMPを有効にします。大量のビルドエラーが発生しますので、1つずつやっつけます。

コンパイルエラー: arch_curr_cpu

環境や利用するバージョンによりますが、最初に目にするのはarch_curr_cpu() に関するコンパイルエラーだと思われます。

arch_curr_cpu() が未定義のときに出るエラー

../include/sys/arch_interface.h:367:28: warning: 'arch_curr_cpu' declared 'static' but never defined [-Wunused-function]

static inline struct _cpu *arch_curr_cpu(void);

^~~~~~~~~~~~~

この関数は、現在のCPU(= 実行中のCPU)の情報を返します。RISC-Vにはmhartidという自身のHART IDを取得できるCSR(Control and Status Registers)が規格で定められており、この手の処理は楽に実装できます。

arch_curr_cpu() の実装

// zephyr/include/arch/riscv/arch_inlines.h

static inline uint32_t z_riscv_hart_id(void)

{

uint32_t hartid;

__asm__ volatile ("csrr %0, mhartid" : "=r"(hartid));

return hartid;

}

static inline struct _cpu *arch_curr_cpu(void)

{

#ifdef CONFIG_SMP

uint32_t hartid = z_riscv_hart_id();

return &_kernel.cpus[hartid];

#else

return &_kernel.cpus[0];

#endif

}

他のアーキテクチャを見る限りarch_inlines.hに定義するのが良さそうですが、RISC-V向けには存在しません。新たに追加しましょう。ヘッダファイルを追加したら、親玉のarch_inlines.hに #includeを追加します。

arch_curr_cpu() の実装(続き)

// zephyr/include/arch/arch_inlines.h

...

#if defined(CONFIG_X86) || defined(CONFIG_X86_64)

#include <arch/x86/arch_inlines.h>

#elif defined(CONFIG_ARC)

#include <arch/arc/arch_inlines.h>

#elif defined(CONFIG_XTENSA)

#include <arch/xtensa/arch_inlines.h>

#elif defined(CONFIG_RISCV) //★この2行を追加する

#include <arch/riscv/arch_inlines.h> //★

#endif

このヘッダは明示的に #includeしなくても常にインクルードされます。

リンクエラー: arch_start_cpu

メインCPU以外のCPU(2つ目以降のCPU)を起動するための関数です。SMPモードの他、非SMPモード(※)でも使います。今はCPU 1つで動かすので、とりあえず空関数を定義します。

関数はどこに定義しても動きますが、他アーキテクチャの実装を見るとSMP関連の関数は1つのCソースファイルにまとめた方が良さそうなので、新たにcpu_smp.cを作成します。

arch_start_cpu() の実装(仮)

// zephyr/arch/riscv/core/CMakeLists.txt

zephyr_library_sources(

cpu_idle.c

cpu_smp.c ★足す★

fatal.c

irq_manage.c

isr.S

prep_c.c

reset.S

swap.S

thread.c

)

// zephyr/arch/riscv/core/cpu_smp.c

void arch_start_cpu(int cpu_num, k_thread_stack_t *stack, int sz,

arch_cpustart_t fn, void *arg)

{

}

ZephyrというかCMakeのルールですけども、新たにソースコードを追加した場合、CMakeLists.txtにファイル名を追加しコンパイル対象に指定する必要があります。特定のCONFIG_* が定義されたときだけコンパイルすることも可能ですが、今回は不要です。

(※)Zephyrのマルチプロセッサモードには、SMPモードと非SMPモードがあります。SMPモードは、互いのプロセッサ間でIPI(Inter-Processor Interrupt)を用いて制御します。非SMPモードでは、互いのプロセッサのことは何も考慮せず動作します。

リンクエラー: smp_timer_init

これはSMP用のタイマーの初期化関数です。タイマーのハードウェア構成はアーキテクチャによって様々で、一様に「こう実装すべき」という指針はありません。今はCPU 1つで動かすので、とりあえず空関数を定義します。

smp_timer_init() を追加(仮)

// zephyr/drivers/timer/riscv_machine_timer.c

...

void smp_timer_init(void)

{

}

今回はRISC-VのPrivilege modeのタイマーが実装対象です。タイマードライバはriscv_machine_timer.cになります。

長くなってきたので、続きは次回。

コメント一覧

- コメントはありません。

この記事にコメントする

この記事にコメントする

2020年10月11日

Zephyr OSで遊ぼう その20 - SMP対応CPUコア数1、ビルドエラーの対処2

目次: Zephyr

SMP対応の序盤、ビルドエラー対処の続きです。

オフセットマクロ

ビルドの難所です。CONFIG_SMPを有効にするとisr.Sで大量にエラーが出ます。

_kernel_offset_* の未定義エラー

zephyr/arch/riscv/core/isr.S:305: Error: illegal operands `lw sp,_kernel_offset_to_irq_stack(t2)'

zephyr/arch/riscv/core/isr.S:316: Error: illegal operands `lw t3,_kernel_offset_to_nested(t2)'

zephyr/arch/riscv/core/isr.S:376: Error: illegal operands `sw t2,_kernel_offset_to_nested(t1)'

zephyr/arch/riscv/core/isr.S:463: Error: illegal operands `lw t1,(0x78+___ready_q_t_cache_OFFSET)(t0)'

zephyr/arch/riscv/core/isr.S:468: Error: illegal operands `sw t1,_kernel_offset_to_current(t0)'

原因は_kernel_offset_* 系のオフセットマクロが未定義になるためです。

_kernel_offset_* の定義箇所

// zephyr/kernel/include/offsets_short.h

#ifndef CONFIG_SMP

/* Relies on _kernel.cpu being the first member of _kernel and having 1 element

*/

#define _kernel_offset_to_nested \r (___cpu_t_nested_OFFSET)

#define _kernel_offset_to_irq_stack \r (___cpu_t_irq_stack_OFFSET)

#define _kernel_offset_to_current \r (___cpu_t_current_OFFSET)

#endif /* CONFIG_SMP */

#define _kernel_offset_to_idle \r (___kernel_t_idle_OFFSET)

#define _kernel_offset_to_current_fp \r (___kernel_t_current_fp_OFFSET)

#define _kernel_offset_to_ready_q_cache \r (___kernel_t_ready_q_OFFSET + ___ready_q_t_cache_OFFSET)

...

// zephyr/include/kernel_offsets.h

...

#ifndef CONFIG_SMP

GEN_OFFSET_SYM(_ready_q_t, cache);

#endif

当たり前ですが、この #ifdefを外すだけではSMPは動きません。対策方法を理解するには、Zephyrのカーネル構造体の内部に、少しだけ立ち入る必要があります。

カーネル構造体(CPUが1つの場合)

カーネル構造体は_kernelという名前で何度か出ていましたが、見覚えありますか?なくても全然構わないです。下記のような定義の構造体です。細かい定義はさておき、大事なことはcpusが _kernelの先頭にある、という点です。

_kernelの定義箇所

// zephyr/kernel/sched.c

/* the only struct z_kernel instance */

struct z_kernel _kernel;

// zephyr/include/kernel_structs.h

struct z_kernel {

struct _cpu cpus[CONFIG_MP_NUM_CPUS]; //★_kernelの先頭にcpusがある★

#ifdef CONFIG_SYS_CLOCK_EXISTS

/* queue of timeouts */

sys_dlist_t timeout_q;

#endif

#ifdef CONFIG_SYS_POWER_MANAGEMENT

int32_t idle; /* Number of ticks for kernel idling */

#endif

/*

* ready queue: can be big, keep after small fields, since some

* assembly (e.g. ARC) are limited in the encoding of the offset

*/

struct _ready_q ready_q;

...

// zephyr/include/kernel_structs.h

struct _cpu {

/* nested interrupt count */

uint32_t nested;

/* interrupt stack pointer base */

char *irq_stack;

/* currently scheduled thread */

struct k_thread *current;

/* one assigned idle thread per CPU */

struct k_thread *idle_thread;

...

CPUが1つしか存在しない場合、cpusの要素数は1であり、_kernelの先頭 = cpus[0] の先頭になります。そのため _kernel.cpus[0].currentのオフセット = cpu構造体のcurrentへのオフセット、です。offsets_short.hの定義はこの性質を利用しています。

C言語だとcpus[0] とcpus[i] の違いでしかなく、ありがたみがわかりませんが、アセンブラだと非常に単純かつ高速にオフセットを求めることができます。下記はisr.Sから持ってきた例ですが、_kernel.cpus[0].currentへのアクセスがわずか2命令で実現できます。

CPU数1のとき、_kernelへのアクセスが最適化できる

la t0, _kernel

RV_OP_LOADREG t0, _kernel_offset_to_current(t0)

残念ながらSMPの場合はcpusが1つではありませんから、上記の最適化は使えません。cpus[n] のオフセット、つまりHART ID * sizeof(struct _cpu) を計算する必要があります。

まずはstruct _cpuのオフセットマクロが未定義なので、追加します。ZephyrではGEN_ABSOLUTE_SYM() というマクロが用意されており、アセンブラ用のマクロを生成してくれます。便利ですね。

cpu_tのオフセットマクロの定義

// zephyr/arch/riscv/core/offsets/offsets.c

#ifdef CONFIG_SMP

GEN_ABSOLUTE_SYM(__cpu_t_SIZEOF, sizeof(_cpu_t));

#endif

次にisr.Sのビルドエラーが出ている箇所を直します。

isr.Sの修正方針

// zephyr/arch/riscv/core/isr.S

/*

* xreg0: result &_kernel.cpu[mhartid]

* xreg1: work area

*/

.macro z_riscv_get_cpu xreg0, xreg1

#ifdef CONFIG_SMP

csrr xreg0, mhartid

addi xreg1, x0, __cpu_t_SIZEOF

mul xreg1, xreg0, xreg1

la xreg0, _kernel

add xreg0, xreg0, xreg1

#else

la xreg0, _kernel

#endif

.endm

//(変更前)

/* Get reference to _kernel */

la t1, _kernel

/* Decrement _kernel.cpus[0].nested variable */

lw t2, _kernel_offset_to_nested(t1)

addi t2, t2, -1

sw t2, _kernel_offset_to_nested(t1)

//(変更後)

/* Get reference to _kernel.cpus[n] */

z_riscv_get_cpu t1, t2 //★z_riscv_get_cpuに置き換え★

/* Decrement _kernel.cpus[n].nested variable */

lw t2, ___cpu_t_nested_OFFSET(t1) //★_kernel_offset_to_* から ___cpu_t_*_OFFSETに置き換え★

addi t2, t2, -1

sw t2, ___cpu_t_nested_OFFSET(t1)

修正方針は2つあります。

- cpus[0] -> cpus[n]: _kernel.cpus[n] のアドレスを取得するマクロz_riscv_get_cpuを作成。_kernel = cpus[0] のアドレスを取得しているところをz_riscv_get_cpuで置き換え。

- _kernel_offset_to_* は未定義なので、___cpu_t_*_OFFSETで置き換え。

ここまで直すとビルドが通るはずですが、実はビルドが通るだけでは動きません。次回は実行時のエラーを対策します。

コメント一覧

- コメントはありません。

この記事にコメントする

この記事にコメントする

2020年10月12日

Zephyr OSで遊ぼう その21 - SMP対応CPUコア数1、実行時エラーの対処

目次: Zephyr

SMP対応のうち、ビルドエラーの対処が終わったので、実行時エラーに対処します。

実行時エラー: k_spin_lock

CONFIG_SMPを有効にすると、k_spin_lock() 内でatomic_cas() を呼ぶようになります。するとk_spin_lock() -> atomic_cas() -> z_impl_atomic_cas() -> k_spin_lock() という循環呼び出しが発生し、スタックオーバーフローを起こしてクラッシュします。これはZephyrのバグではなくコンフィグの設定間違いが原因です。

k_spin_lock() の循環呼び出し

// zephyr/include/spinlock.h

static ALWAYS_INLINE k_spinlock_key_t k_spin_lock(struct k_spinlock *l)

{

ARG_UNUSED(l);

k_spinlock_key_t k;

/* Note that we need to use the underlying arch-specific lock

* implementation. The "irq_lock()" API in SMP context is

* actually a wrapper for a global spinlock!

*/

k.key = arch_irq_lock();

#ifdef CONFIG_SPIN_VALIDATE

__ASSERT(z_spin_lock_valid(l), "Recursive spinlock %p", l);

#endif

#ifdef CONFIG_SMP

while (!atomic_cas(&l->locked, 0, 1)) { //★CONFIG_SMPが有効だとatomic_cas() を呼ぶ★

}

#endif

...

// zephyr/include/sys/atomic.h

#ifdef CONFIG_ATOMIC_OPERATIONS_BUILTIN

static inline bool atomic_cas(atomic_t *target, atomic_val_t old_value,

atomic_val_t new_value)

{

return __atomic_compare_exchange_n(target, &old_value, new_value,

0, __ATOMIC_SEQ_CST,

__ATOMIC_SEQ_CST);

}

#elif defined(CONFIG_ATOMIC_OPERATIONS_C) //★既存のRISC-Vボードはこちらが有効になっている★

__syscall bool atomic_cas(atomic_t *target, atomic_val_t old_value,

atomic_val_t new_value);

#else

extern bool atomic_cas(atomic_t *target, atomic_val_t old_value,

atomic_val_t new_value);

#endif

...

// build/zephyr/include/generated/syscalls/atomic.h

static inline bool atomic_cas(atomic_t * target, atomic_val_t old_value, atomic_val_t new_value)

{

#ifdef CONFIG_USERSPACE

if (z_syscall_trap()) {

return (bool) arch_syscall_invoke3(*(uintptr_t *)&target, *(uintptr_t *)&old_value, *(uintptr_t *)&new_value, K_SYSCALL_ATOMIC_CAS);

}

#endif

compiler_barrier();

return z_impl_atomic_cas(target, old_value, new_value); //★ここにくる★

}

...

// zephyr/kernel/CMakeLists.txt

target_sources_ifdef(CONFIG_ATOMIC_OPERATIONS_C kernel PRIVATE atomic_c.c) //★CONFIG_ATOMIC_OPERATIONS_C有効のとき実装はatomic_c.c★

...

// zephyr/kernel/atomic_c.c

bool z_impl_atomic_cas(atomic_t *target, atomic_val_t old_value,

atomic_val_t new_value)

{

k_spinlock_key_t key;

int ret = false;

key = k_spin_lock(&lock); //★循環呼び出し★

if (*target == old_value) {

*target = new_value;

ret = true;

}

k_spin_unlock(&lock, key);

return ret;

}

...

RISC-VのSoCのコンフィグでは大抵CONFIG_ATOMIC_OPERATIONS_Cが有効になっていて、atomic_cas() の実装としてスピンロックを使います。これはSMPと相性が悪く、CONFIG_ATOMIC_OPERATIONS_CとCONFIG_SMPを同時に有効にすると先ほど説明した循環呼び出しが発生してしまいます。

循環呼び出しを防ぐには独自にatomic_cas() を実装する必要がありますが、アトミック操作を自分で実装&検証するのは大変ですから、RISC-Vのアトミック命令(Atomic Extension)とコンパイラの機能を頼ります。

以前追加したQEMU RISC-V 32bit virtpc用のコンフィグをSMPのテスト用に改造します。

ATOMIC_OPERATIONS_* の設定例

# zephyr/soc/riscv/riscv-privilege/rv32-virt/Kconfig.soc

config SOC_QEMU_RV32_VIRT

bool "QEMU RV32 virt SOC implementation"

select ATOMIC_OPERATIONS_C if !SMP # 非SMPのときは従来通り

select ATOMIC_OPERATIONS_BUILTIN if SMP # SMPのときはAtomic Extensionに頼る

コンフィグCONFIG_ATOMIC_OPERATIONS_BUILTINを有効にすると、Zephyrはatomic_cas() の実装として __atomic_compare_exchange_n() ビルトイン関数を使います。ビルトイン関数を使うにはコンパイラのサポートが必要で、今のところ、サポートしているのはGCCのみだと思います。LLVMでも使えるかもしれませんが、未調査です。

これでCONFIG_SMPを有効にしても、エラーやハングアップすることなく、今までどおりに動作するようになったはずです。

コメント一覧

- コメントはありません。

この記事にコメントする

この記事にコメントする

2020年10月13日

Zephyr OSで遊ぼう その22 - SMP対応CPUコア数1、HART 0以外で動かす、動作確認環境

目次: Zephyr

前回はCONFIG_SMPのビルドエラーと実行時エラーに対応しました。以前書いたとおり、SMP対応は下記の手順で進めていますので、再掲します。

- SMPの前提条件、新しいコンテキストスイッチ方式に対応する(CONFIG_USE_SWITCH, CONFIG_USE_SWITCH_SUPPORTED)

- SMPに対応する(CONFIG_SMP)、ただしCPUコア数は1

- (今ここ)先頭ではないコア(mhartid != 0)で動作させる、ただしCPUコア数は1

- CPUコア数を1以上にする(CONFIG_SMP)

前回までで2番目の項目が終わったところです。今回はコア数を増やして先頭以外のコアで実行します。

動作確認の環境

Zephyrを書き換える前に、変更した効果が確認できる環境を作りましょう。サンプルのsynchronizationを少し改造してHART IDを表示します。

スレッド名を表示させる機能を加える

// zephyr/samples/synchronization/src/main.c

void helloLoop(const char *my_name,

struct k_sem *my_sem, struct k_sem *other_sem)

{

const char *tname;

while (1) {

int id = z_riscv_hart_id(); //★HART IDを取得★

/* take my semaphore */

k_sem_take(my_sem, K_FOREVER);

/* say "hello" */

tname = k_thread_name_get(k_current_get());

if (tname != NULL && tname[0] != '\0') {

printk("%d: %s: Hello World from %s!\n",

id, tname, CONFIG_BOARD); //★HART IDを一緒に表示する★

} else {

printk("%d: %s: Hello World from %s!\n",

id, my_name, CONFIG_BOARD); //★HART IDを一緒に表示する★

}

今回は変更してもしなくても構わないですが、カーネルコンフィグを変えるとk_thread_name_get() でスレッド名が取得できるようになります。スレッドを多数作成したときに便利です。

スレッド名を表示させる設定

$ ninja menuconfig

General Kernel Options --->

Kernel Debugging and Metrics --->

[*] Thread name [EXPERIMENTAL]

動作させると下記のような表示になるはずです。

変更前の実行結果

$ mkdir build $ cd build $ cmake -G Ninja -DBOARD=qemu_rv32_virt ../samples/synchronization/ ... $ ninja ... $ qemu-system-riscv32 -nographic -machine virt -net none -chardev stdio,id=con,mux=on -serial chardev:con -mon chardev=con,mode=readline -kernel zephyr/zephyr.elf -cpu rv32 -smp cpus=1 -bios none ** Booting Zephyr OS build zephyr-v2.4.0-546-g720718653f92 *** 0: thread_a: Hello World from QEMU RV32 virt board! 0: thread_b: Hello World from QEMU RV32 virt board! 0: thread_a: Hello World from QEMU RV32 virt board! 0: thread_b: Hello World from QEMU RV32 virt board! ...

HART ID = 0で実行されていることがわかります。

続きは次回です。

コメント一覧

- コメントはありません。

この記事にコメントする

この記事にコメントする

2020年10月14日

Zephyr OSで遊ぼう その23 - SMP対応CPUコア数1、HART 0以外で動かす

目次: Zephyr

前回はHART 0以外で動かす際に、動作確認が必要なので準備を行いました。今回はHART 0以外で動かします。

実行するHARTを一時的にずらす

一番簡単なやり方は、ブート時の判定条件を変えることだと思います。通常はHART IDが0だったら起動しますが、0じゃないHARTのときに起動するように変更します。この変更は最終的には不要なので、あとで元に戻すのを忘れないようにしてください。

変更前の実行結果

// zephyr/arch/riscv/core/reset.S

...

SECTION_FUNC(TEXT, __initialize)

/*

* This will boot master core, just halt other cores.

* Note: need to be updated for complete SMP support

*/

csrr a0, mhartid

addi a0, a0, -3 //★HART ID - 3 = 0なら実行する、つまりHART ID 3で実行する★

beqz a0, boot_master_core

...

ZephyrのCPUコア数はmenuconfigから変更可能です。なぜかは知りませんが、最大4コアらしいです。

CPU数の変更

$ ninja menuconfig

General Kernel Options --->

SMP Options --->

(4) Number of CPUs/cores

実行してみます。QEMUの -smp cpus=1オプションをcpus=4に変更して4コアで実行します。

変更前の実行結果

$ qemu-system-riscv32 -nographic -machine virt -net none -chardev stdio,id=con,mux=on -serial chardev:con -mon chardev=con,mode=readline -kernel zephyr/zephyr.elf -cpu rv32 -smp cpus=4 -bios none ** Booting Zephyr OS build zephyr-v2.4.0-546-g720718653f92 *** 3: thread_a: Hello World from QEMU RV32 virt board!

HART IDは変わりました。しかしスレッドAからスレッドBに切り替わらず、ハングアップしてしまいます。原因はタイマー割り込みがHART ID 0以外に入らないからです。Zephyrはタイマー割り込みによってカーネルの内部時間(Tick)を更新する他、割り込みを契機にコンテキストスイッチを行っています。

タイマーのSMP対応

Zephyrでは通常の定期的なタイマー割り込みと、Tickless Timerという不定期なタイマー割り込みの仕組みがあります。通常のタイマーの場合、一定時間ごとにタイマー割り込みを発生(例えば10msごとなど)させ、1Tickずつ時間を進めます。実装は単純ですが、用もなくタイマー割り込みが発生するため、消費電力や処理性能に悪影響を及ぼします。

Tickless Timerの場合、各CPUが「最後に割り込みが発生した時刻」を記録しておいて、タイマー、タイマー以外の割り込みが発生した際に、前回の割り込みからどれだけ時間が経過したか、つまり、何Tick経過したか?を計算して、一気に時間を進めます。また「次のタイマー割り込みの設定」は、できるだけ遠く(現在時刻 +1 Tick)に設定して、無用なタイマー割り込みが発生しないように工夫されています。

「最後に割り込みが発生した時刻」と「次のタイマー割り込みの設定」はCPUが割り込みを受けたタイミングによって値が変わり、全CPUで共有する値ではありませんから、CPUごとに専用の場所を用意する必要があります。

タイマーのSMP対応

// zephyr/drivers/timer/riscv_machine_timer.c(変更前)

static struct k_spinlock lock;

static uint64_t last_count;

static void set_mtimecmp(uint64_t time)

{

#ifdef CONFIG_64BIT

*(volatile uint64_t *)RISCV_MTIMECMP_BASE = time;

#else

volatile uint32_t *r = (uint32_t *)RISCV_MTIMECMP_BASE;

// zephyr/drivers/timer/riscv_machine_timer.c(変更後)

#define RISCV_MTIMECMP (RISCV_MTIMECMP_BASE + (uintptr_t)z_riscv_hart_id() * 8) //★「次のタイマー割り込みの設定」★

#define last_count last_count_mp[z_riscv_hart_id()] //★「最後に割り込みが発生した時刻」★

static struct k_spinlock lock;

static uint64_t last_count_mp[CONFIG_MP_NUM_CPUS]; //★CPUの数だけ配列を確保★

static void set_mtimecmp(uint64_t time)

{

#ifdef CONFIG_64BIT

*(volatile uint64_t *)RISCV_MTIMECMP = time;

#else

volatile uint32_t *r = (uint32_t *)RISCV_MTIMECMP;

今回のSMP対応ではMTIMECMPレジスタの幅が64bitであることがわかれば、動作の詳細を知らなくても読み進められると思います。

仕様が気になる場合は、SiFive Core Local Interruptor(CLINT)の仕様を参照ください。CLINTはFE310もしくはFU540のマニュアルに載っています。FE310はシングルコア、FU540はマルチコアです(FE310-G002 Manual, FU540-C000 Manual)。

効果の確認

以上の対応でHART ID 0以外もタイマー割り込みが入るようになり、スケジューラが動作するようになったはずです。

変更後の実行結果

$ qemu-system-riscv32 -nographic -machine virt -net none -chardev stdio,id=con,mux=on -serial chardev:con -mon chardev=con,mode=readline -kernel zephyr/zephyr.elf -cpu rv32 -smp cpus=4 -bios none ** Booting Zephyr OS build zephyr-v2.4.0-546-g720718653f92 *** 3: thread_a: Hello World from QEMU RV32 virt board! 3: thread_b: Hello World from QEMU RV32 virt board! 3: thread_a: Hello World from QEMU RV32 virt board! 3: thread_b: Hello World from QEMU RV32 virt board! ...

HART ID = 3で実行されています。やったね。以降、実行するHARTを一時的にずらす変更は不要なので、元に戻すことを忘れないようにしてください。

コメント一覧

- コメントはありません。

この記事にコメントする

この記事にコメントする

2020年10月15日

Zephyr OSで遊ぼう その24 - SMP対応CPUコア数4、マルチコアブート

目次: Zephyr

CONFIG_SMP有効、1コア、HART ID != 0の動作確認をしました。以前書いたとおり、SMP対応は下記の手順で進めていますので、再掲します。

- SMPの前提条件、新しいコンテキストスイッチ方式に対応する(CONFIG_USE_SWITCH, CONFIG_USE_SWITCH_SUPPORTED)

- SMPに対応する(CONFIG_SMP)、ただしCPUコア数は1

- 先頭ではないコア(mhartid != 0)で動作させる、ただしCPUコア数は1

- (今ここ)CPUコア数を1以上にする(CONFIG_SMP)

現在3番目の項目が終わったところです。いよいよ最後です。SMP対応の本丸である、マルチコアブート、IPIの対応を進めます。

マルチコアブート(マスター側)

前回(2020年10月10日の日記参照)、空関数で実装したarch_start_cpu() を真面目に実装するときが来ました。HART 0をマスターコア、それ以外をスレーブコアとします。マスターコアはarch_start_cpu() を呼びスレーブコアを1つずつ起床します。

マルチコアブート(マスター側)、arch_start_cpu() の実装

// zephyr/kernel/smp.c

void z_smp_init(void)

{

(void)atomic_clear(&start_flag);

#if defined(CONFIG_SMP) && (CONFIG_MP_NUM_CPUS > 1)

for (int i = 1; i < CONFIG_MP_NUM_CPUS; i++) {

arch_start_cpu(i, z_interrupt_stacks[i], CONFIG_ISR_STACK_SIZE,

smp_init_top, &start_flag); //★スレーブコアの数だけarch_start_cpu() を呼ぶ★

}

#endif

(void)atomic_set(&start_flag, 1);

}

// zephyr/arch/riscv/core/cpu_smp.c

static volatile struct {

arch_cpustart_t fn;

void *arg;

} riscv_cpu_cfg[CONFIG_MP_NUM_CPUS];

volatile uintptr_t riscv_init_flag;

volatile void *riscv_init_sp;

//★マスターコアが実行★

void arch_start_cpu(int cpu_num, k_thread_stack_t *stack, int sz,

arch_cpustart_t fn, void *arg)

{

riscv_cpu_cfg[cpu_num].fn = fn;

riscv_cpu_cfg[cpu_num].arg = arg;

/* Signal to slave core with initial sp. */

riscv_init_sp = Z_THREAD_STACK_BUFFER(stack) + sz; //★スタックポインタの初期値★

riscv_init_flag = cpu_num; //★スレーブコアを起床★

/* Wait for slave core */

while (riscv_init_flag == cpu_num) { //★スレーブコアが起床するまでビジーウェイト★

;

}

}

引数の意味はCPU番号cpu_num、スタックの先頭アドレスstack、スタックのサイズsz、スレーブコアが実行する関数のポインタfn、関数の引数argです。fnとargは後でスレーブコアが使うので配列riscv_cpu_cfg[] に保存します。

スタックポインタとCPU番号はスレーブコアのブート部分で参照するので、グローバル変数に保存します。riscv_init_flag, riscv_init_spは配列にしなくても上書きされる心配はありません。マスターコアはスレーブコアを一度に1コアずつ起こすように実装するので、複数のスレーブコアが同時に同じスタックを使って異常動作する事態は発生し得ないからです。スレーブコア側の実装も見ていただければわかるはず、です。

マルチコアブート(スレーブ側)

リセット後、スレーブコアは一度に全コアが起動します。ブートコードの途中で、マスターコアから設定されるフラグを待つように実装します。下記コードでいえばboot_slave_coreのところです

マルチコアブート(スレーブ側)、ブートコードの実装

SECTION_FUNC(TEXT, __initialize)

/*

* This will boot master core, just halt other cores.

* Note: need to be updated for complete SMP support

*/

csrr a0, mhartid

beqz a0, boot_master_core //★HART 0はマスターコア★

li a1, CONFIG_MP_NUM_CPUS //★CONFIG_MP_NUM_CPUSより小さいHART IDならスレーブコア★

blt a0, a1, boot_slave_core

loop_slave_core: //★CONFIG_MP_NUM_CPUS以上のHART IDがあったら、wfiでスリープ状態にさせる★

wfi

j loop_slave_core

boot_slave_core:

/* Wait for signal from master core */

la t0, riscv_init_flag

RV_OP_LOADREG t1, (t0)

bne a0, t1, boot_slave_core //★riscv_init_flagに自分のHART IDが設定されるまで待つ★

/* Setup stack */

la t1, riscv_init_sp

RV_OP_LOADREG sp, (t1) //★スタックポインタ初期化★

/* Notify to master core */

RV_OP_STOREREG x0, (t0) //★マスターコアにブート完了を知らせる★

j z_riscv_slave_start

...

// zephyr/arch/riscv/core/cpu_smp.c

//★スレーブコアが実行★

void z_riscv_slave_start(int cpu_num)

{

#if defined(CONFIG_RISCV_SOC_INTERRUPT_INIT)

soc_interrupt_init();

#endif

riscv_cpu_cfg[cpu_num].fn(riscv_cpu_cfg[cpu_num].arg); //★arch_start_cpu() で指定された関数と引数★

}

スレーブコアは全てが同時にriscv_init_flagをチェックしますが、riscv_init_flag == 自身のHART IDと一致しない限り永久に待つため、flagチェック以降の処理に進むことはありません。この機構により同じスタックを2つ以上のスレーブコアが同時に使ってしまうことを避けています。

以上で、マルチコアが動き始めました。続きは次回。

コメント一覧

- コメントはありません。

この記事にコメントする

この記事にコメントする

2020年10月16日

Zephyr OSで遊ぼう その25 - SMP対応CPUコア数4、IPIの実装

目次: Zephyr

前回はマルチコアのブート処理を実装しました。今回はIPI (Inter-Processor Interrupt、プロセッサ間割り込み) を実装します。長きに渡ったSMP対応もようやく終盤です。

IPIとは

IPIとはInter-Processor Interrupt、プロセッサ間割り込みのことで、SMPの核となる機能です。プロセッサ間で何かイベントを伝えたい(今回の場合はスレッドスケジューラを動かしてほしい)ときにIPIを発生させます。

RISC-V Privilegeの場合、IPIを発生させるにはCLINTを使います。CLINTのmsipレジスタの最下位ビットは、それぞれのHARTのmipレジスタのMSIPビットに繋がっています。平たく言えばmsipレジスタに1を書き込むと他のHARTにソフトウェア割り込みが発生する仕組みです。

CLINTはタイマードライバの実装のときに出てきました(2020年10月14日の日記参照)。IPIの実装は、他アーキテクチャだとzephyr/arch/*/coreの下に実装していることが多いですが、RISC-Vの場合はタイマードライバzephyr/drivers/timer/riscv_machine_timer.cに実装すると早いです。このやり方で合っているのかはちょっとわかりません。割り込みコントローラとして新たに実装した方が筋が良さそうではあります。

IPI発生側の実装

IPIの実装を発生させる側と受け取る側に分けて説明します。

IPI発生側の実装 (arch_sched_ipi)

// zephyr/drivers/timer/riscv_machine_timer.c

#define RISCV_MSIP_OTHER(id) (RISCV_MSIP_BASE + (uintptr_t)(id) * 4)

#define RISCV_MSIP RISCV_MSIP_OTHER(z_riscv_hart_id())

...

#ifdef CONFIG_SMP

void arch_sched_ipi(void)

{

uint32_t id = z_riscv_hart_id();

for (int i = 0; i < CONFIG_MP_NUM_CPUS; i++) {

volatile uint32_t *r = (uint32_t *)RISCV_MSIP_OTHER(i);

if (i == id)

continue; //★自分自身には割り込みを発生させない★

*r = 1;

}

}

...

発生させる側の実装はarch_sched_ipi() 関数を定義して、自分以外のHARTに割り込みを発生させます。シンプルで良いですね。

IPIを発生させる処理も確認します。何箇所かありますが、短めのものを例として挙げます。

IPI発生側の実装 (スケジューラ)

// zephyr/kernel/sched.c

static void ready_thread(struct k_thread *thread)

{

if (z_is_thread_ready(thread)) {

sys_trace_thread_ready(thread);

_priq_run_add(&_kernel.ready_q.runq, thread);

z_mark_thread_as_queued(thread);

update_cache(0);

#if defined(CONFIG_SMP) && defined(CONFIG_SCHED_IPI_SUPPORTED)

arch_sched_ipi(); //★ここで呼ばれている★

#endif

}

}

コンフィグCONFIG_SMPは既に有効にしていますが、それ以外にもCONFIG_SCHED_IPI_SUPPORTEDを有効にする必要があるようです。

IPIのサポートを追加する

// zephyr/drivers/timer/Kconfig

config RISCV_MACHINE_TIMER

bool "RISCV Machine Timer"

depends on SOC_FAMILY_RISCV_PRIVILEGE

select TICKLESS_CAPABLE

select SCHED_IPI_SUPPORTED #★この行を足す★

help

This module implements a kernel device driver for the generic RISCV machine

timer driver. It provides the standard "system clock driver" interfaces.

今回IPIの機構を実装したのはタイマードライバですので、タイマーのKconfigに追加しています。

IPI受信側の実装

IPIを受け取る側の実装です。マスターコアとスレーブコアで呼ばれる関数が違う点は少しややこしいですが、基本的にやることは一緒です。前回(2020年10月10日の日記参照)、空関数で実装したsmp_timer_init() を真面目に実装するときが来ました。

IPI受信側の実装(割り込みハンドラ)

#ifdef CONFIG_SMP

void z_riscv_sched_ipi(void);

static void soft_isr(const void *arg)

{

volatile uint32_t *r = (uint32_t *)RISCV_MSIP;

ARG_UNUSED(arg);

*r = 0; //★ソフトウェア割り込みをクリア★

z_riscv_sched_ipi(); //★IPIテスト用の関数(後日に説明予定)今はリンクエラーになるはずなので、コメントアウトしてOK★

}

#endif

//★マスターコア用のタイマー初期化関数★

int z_clock_driver_init(const struct device *device)

{

ARG_UNUSED(device);

IRQ_CONNECT(RISCV_MACHINE_TIMER_IRQ, 0, timer_isr, NULL, 0);

last_count = mtime();

set_mtimecmp(last_count + CYC_PER_TICK);

irq_enable(RISCV_MACHINE_TIMER_IRQ);

#ifdef CONFIG_SMP

IRQ_CONNECT(RISCV_MACHINE_SOFT_IRQ, 0, soft_isr, NULL, 0); //★ソフトウェア割り込みの割り込みハンドラを設定する★

irq_enable(RISCV_MACHINE_SOFT_IRQ); //★ソフトウェア割り込み有効★

#endif

return 0;

}

...

//★スレーブコア用のタイマー初期化関数★

//★マスターコアが割り込みハンドラの設定をするので、割り込みを有効にするだけに留める★

void smp_timer_init(void)

{

last_count = mtime();

set_mtimecmp(last_count + CYC_PER_TICK);

irq_enable(RISCV_MACHINE_TIMER_IRQ);

irq_enable(RISCV_MACHINE_SOFT_IRQ);

}

#endif /* CONFIG_SMP */

割り込みを有効にして、ソフトウェア割り込みハンドラでCLINTのmsipレジスタをクリアします。msipのクリアを忘れると割り込みハンドラが終わった直後、またすぐソフトウェア割り込みが入って、ハンドラが呼ばれて、割り込みが入って、ハンドラが呼ばれて、、、を繰り返してしまい処理が先に進まなくなって、ハングします。

動作確認

前回作成した環境を流用して動作確認します。

IPI受信側の実装(割り込みハンドラ)

$ ninja run [0/1] To exit from QEMU enter: 'CTRL+a, x'[QEMU] CPU: riscv32 *** Booting Zephyr OS build zephyr-v2.4.0-546-g720718653f92 *** 1: thread_a: Hello World from QEMU RV32 virt board! 2: thread_b: Hello World from QEMU RV32 virt board! 0: thread_a: Hello World from QEMU RV32 virt board! 2: thread_b: Hello World from QEMU RV32 virt board! 1: thread_a: Hello World from QEMU RV32 virt board! 3: thread_b: Hello World from QEMU RV32 virt board! 1: thread_a: Hello World from QEMU RV32 virt board! ...

やった!動きました。スレッドがHART 0だけでなく、別のHARTでも実行されている様子がわかります。

リグレッションテストについては、また次回。

コメント一覧

- コメントはありません。

この記事にコメントする

この記事にコメントする

2020年10月17日

Zephyr OSで遊ぼう その26 - SMP対応、リグレッションテストの準備

目次: Zephyr

前回はSMPに対応しました。今回はリグレッションテストを行う準備をします。

リグレッションテストの方法

Zephyrにはsanitycheckというツールが用意されています。テストレポートやテスト用バイナリが生成されるので、Zephyrのトップディレクトリではなく、空ディレクトリを作ってから実行すると良いです。オプション -pでテストしたいプラットフォームを指定します。

sanitycheckの実行

$ mkdir __tmp $ cd __tmp $ sanitycheck -p qemu_riscv32 INFO - JOBS: 16 INFO - Building initial testcase list... INFO - 928 test configurations selected, 752 configurations discarded due to filters. INFO - Adding tasks to the queue... ...

いちいちsanitycheckを全部実行するとかなり時間が掛かります。テストにはタグが付いていて、sanitycheckはオプション -tで特定のタグが付いたテストのみを実行できます。便利ですね。

タグはどこから来ているかというとtestsディレクトリの下に存在するtestcase.yamlというファイルに書いてあります。

テストのタグ

// zephyr/kernel/smp/testcase.yaml

tests:

kernel.multiprocessing.smp:

tags: smp //★これがタグ★

filter: (CONFIG_MP_NUM_CPUS > 1) //★フィルタ、この条件が真でないとテストがスキップされる★

SMP系のテストにはsmpというタグが付いているので、-t smpと指定します。

sanitycheckの実行(SMP系)、スキップされる

$ sanitycheck -p qemu_riscv32 -t smp INFO - JOBS: 16 INFO - Building initial testcase list... INFO - 928 test configurations selected, 925 configurations discarded due to filters. INFO - Adding tasks to the queue... INFO - Total complete: 3/ 3 100% skipped: 3, failed: 0 INFO - 0 of 0 tests passed (0.00%), 0 failed, 928 skipped with 0 warnings in 1.95 seconds INFO - In total 0 test cases were executed on 1 out of total 292 platforms (0.34%) INFO - 0 tests executed on platforms, 0 tests were only built.

残念ながらテストは全てスキップされてしまいます。原因はqemu_riscv32ボードはSMPに対応していない(CONFIG_SMPをselectしない)ため、testcase.yamlに書かれたフィルタに引っかかって除外されるからです。

俺の作ったボードはどこ行った?

先日作成したqemu_rv32_virtボードならばCONFIG_SMPが有効なので、テストが実行されるはずです。

sanitycheckの実行(SMP系)、実行されない

$ sanitycheck -p qemu_rv32_virt -t smp INFO - JOBS: 16 INFO - Building initial testcase list... INFO - 0 test configurations selected, 0 configurations discarded due to filters. INFO - Adding tasks to the queue... INFO - 0 of 0 tests passed (0.00%), 0 failed, 0 skipped with 0 warnings in 0.65 seconds INFO - In total 0 test cases were executed on 0 out of total 291 platforms (0.00%) INFO - 0 tests executed on platforms, 0 tests were only built.

ダメですね。こういうときは既存のボードと見比べて差分を見るとわかりやすいです。どうやらboard.cmake, qemu_rv32_virt.yamlを作らないと、ボードが認識されないようです。

sanitycheckの実行に必要なファイルを追加

# zephyr/boards/riscv/qemu_rv32_virt/board.cmake

# SPDX-License-Identifier: Apache-2.0

set(EMU_PLATFORM qemu)

set(QEMU_binary_suffix riscv32)ARCH riscv32)

ARCH

-nographic

-machine virt

-cpu rv32

-bios none

)

board_set_debugger_ifnset(qemu)

// zephyr/boards/riscv/qemu_rv32_virt/qemu_rv32_virt.yaml

identifier: qemu_rv32_virt

name: QEMU RISCV32 virt target

type: qemu

simulation: qemu

arch: riscv32

ram: 256

toolchain:

- zephyr

- xtools

testing:

default: true

ignore_tags:

- net

- bluetooth

もう一度実行します。

sanitycheckの実行(SMP系)、実行できた

$ sanitycheck -p qemu_rv32_virt -t smp INFO - JOBS: 16 INFO - Building initial testcase list... INFO - 928 test configurations selected, 925 configurations discarded due to filters. INFO - Adding tasks to the queue... ERROR - qemu_rv32_virt tests/kernel/smp/kernel.multiprocessing.smp FAILED: Timeout ERROR - see: zephyr/__tmp/sanity-out/qemu_rv32_virt/tests/kernel/smp/kernel.multiprocessing.smp/handler.log INFO - Total complete: 1/ 3 33% skipped: 0, failed: 1 ERROR - qemu_rv32_virt tests/kernel/spinlock/kernel.multiprocessing.spinlock FAILED: Failed ERROR - see: zephyr/__tmp/sanity-out/qemu_rv32_virt/tests/kernel/spinlock/kernel.multiprocessing.spinlock/handler.log INFO - Total complete: 3/ 3 100% skipped: 0, failed: 2 INFO - 1 of 3 tests passed (33.33%), 2 failed, 925 skipped with 0 warnings in 72.61 seconds INFO - In total 13 test cases were executed on 1 out of total 292 platforms (0.34%) INFO - 2 tests executed on platforms, 1 tests were only built.

いくつかのテストがFAILEDしている、すなわちデグレードしていることを示していますが、ひとまずテストは実行できました。次回はデグレードした箇所を直します。

コメント一覧

- コメントはありません。

この記事にコメントする

この記事にコメントする

2020年10月18日

Zephyr OSで遊ぼう その27 - SMP対応、デグレードの修正

目次: Zephyr

前回はリグレッションテストの実行環境を整備しました。今回はリグレッションテストで見つけたバグを修正します。

バグその1、割り込みハンドラ判定関数

テストtests/kernel/smp/kernel.multiprocessing.smpが失敗しています。

リグレッションテストのエラー、arch_is_in_isr()

ASSERTION FAIL [!arch_is_in_isr()] @ ZEPHYR_BASE/kernel/sched.c:1209

テスト対象のarch_is_in_isr() の実装を見ると、シングルコアを前提とした実装になっています。

割り込みハンドラ判定関数の修正

// zephyr/arch/riscv/include/kernel_arch_func.h

static inline bool arch_is_in_isr(void)

{

return _kernel.cpus[0].nested != 0U; //★シングルコア前提になっている★

}

// (修正後)

static inline bool arch_is_in_isr(void)

{

return arch_curr_cpu()->nested != 0U;

}

直し方はarch_curr_cpu() に置き換えるだけで良さそうです。

バグその2、IPIのテスト用コンフィグへの対応

他のテストではsched_ipi_has_calledが0のままらしく、怒られています。

リグレッションテストのエラー、sched_ipi_has_called

Assertion failed at ZEPHYR_BASE/tests/kernel/smp/src/main.c:602: test_smp_ipi: (sched_ipi_has_called != 0 is false)

テスト対象のsched_ipi_has_calledをカウントアップする処理は下記のとおりです。

sched_ipi_has_calledの実装箇所

// zephyr/kernel/sched.c

#ifdef CONFIG_SMP

void z_sched_ipi(void)

{

/* NOTE: When adding code to this, make sure this is called

* at appropriate location when !CONFIG_SCHED_IPI_SUPPORTED.

*/

#ifdef CONFIG_TRACE_SCHED_IPI

z_trace_sched_ipi();

#endif

}

// zephyr/tests/kernel/smp/src/main.c

#ifdef CONFIG_TRACE_SCHED_IPI

/* global variable for testing send IPI */

static volatile int sched_ipi_has_called;

void z_trace_sched_ipi(void)

{

sched_ipi_has_called++;

}

コンフィグCONFIG_TRACE_SCHED_IPIが有効になっているときは、カーネルがz_trace_sched_ipi() を呼び出します。テストではCONFIG_TRACE_SCHED_IPIを有効にするとともに、この関数を定義して、カーネルから正常にコールバックされるかどうかを見ているようです。

以前(2020年10月16日の日記参照)、IPIのハンドラを実装した際にコメントアウトしてくれ、と言っていた部分がありました。あの部分が役に立ちます。

IPIハンドラからz_sched_ipi() を呼ぶ

// zephyr/drivers/timer/riscv_machine_timer.c

#ifdef CONFIG_SMP

void z_riscv_sched_ipi(void);

static void soft_isr(const void *arg)

{

volatile uint32_t *r = (uint32_t *)RISCV_MSIP;

ARG_UNUSED(arg);

*r = 0;

z_riscv_sched_ipi(); //★この行を足す★

}

#endif

// zephyr/arch/riscv/core/cpu_smp.c

#ifdef CONFIG_SMP

void z_riscv_sched_ipi(void)

{

z_sched_ipi();

}

#endif

本当は直接z_sched_ipi() を呼べば良いんですが、drivers以下のソースコードからはz_sched_ipi() を呼ばない方が良さそう(関数プロトタイプが見えない)だったので、arch/riscvを経由させる変な実装になっています。どう実装するのが正しいんでしょうねえ?

これでSMP系のテストを通過しました。良かった良かった。

コメント一覧

- コメントはありません。

この記事にコメントする

この記事にコメントする

2020年10月21日

テスラはバッテリーも作ります

【速報】テスラ「バッテリー・デー」のポイントを解説 - EVsmartブログ を読んで。

約1か月前のニュースですが「電池は自分で作るんで!さよなら!!」と鮮やかにポイ捨てされたパナソニックさん。

一緒に5000億の工場(ギガファクトリー1)を作り始めた(※1)かと思いきや、投資回収どころか、工場完成してないのに縁切り宣言を始める辺り、テスラは気が短すぎます。この決断スピードには、パナソニックはとても付いていけないでしょう。

今だから思いますが、ギガファクトリー1はうまく(?)できていて、セル:パナソニック、アセンブリ:テスラの分担となっていますので、テスラは離脱してもほぼ損害がありません。テスラは最初からバッテリー自社生産を狙っていたのでは?とすら感じます。

いずれにせよ困るのはパナソニックで、テスラに離脱されると、大量の2170セル生産能力が余ります(※2)。18650に転換してもテスラ並みの需要を持つ顧客はいるでしょうか?

(※1)ギガファクトリー1は合弁で建てているので、パナソニックとテスラの負担割合はわかりません。さすがにゼロってことはないでしょう。

(※2)ギガファクトリー1は、テスラ専用の2170(直径21mm x高さ70mm)という微妙にでかいバッテリーセルを作っており、標準的な18650(18mm x 65.0mm)セル使う機器には使いまわし効かないように見えます。

三洋に続くパナソニック爆死案件なのか?

5年位前にギガファクトリー1のニュースを見たときは「テスラと組むなんて、パナソニックも変わったなあ〜」なんて感動しました。パナソニックの社運を賭けた投資、なんてニュースも目にしたものです。

ぼーっとしているとテスラに置いて行かれ、数年後にはギガファクトリー1が、パナソニックの大型失敗案件、砺波CCD(1000億)、尼崎プラズマ(4000億?)、三洋合併(6000億円?)にランクインしてしまいそうです。

完全にテスラに寄りかかって、何も考えてないパナソニックが悪い、ダシにされて当然だろ?っていわれたら、何も言い返せないですが、さすがに合弁作ってハイさようならは、ご無体すぎて可哀想ですね……。

メモ: 技術系の話はFacebookから転記しておくことにした。加筆修正。

コメント一覧

- コメントはありません。

この記事にコメントする

この記事にコメントする

2020年10月23日

ARM - まとめリンク

目次: ARM

ROCK64ブート周りの話のまとめ。

- ROCK64購入

- ROCK64とU-Bootのdistro boot

- ROCK64のU-Bootスクリプトを読む

- ROCK64のカーネルだけ元に戻したい

- Welcome back ROCK64

- ROCK64とTinker BoardのU-Boot設定メモ

- ROCK64をRaspberry Pi 3のケースに無理やり格納

ROCK64オーディオ周りの話のまとめ。

- ROCK64のアナログオーディオ - その1 - I2Sとクロックレジスタ

- ROCK64のアナログオーディオ - その2 - I2SのDMA問題

- ROCK64のアナログオーディオ - その3 - I2S2を認識しない問題解決(DMAチャネル数の問題だった)

- ROCK64のアナログオーディオ - その4 - I2S1が動かない問題解決(クロックゲート定義のバグを直した)

- ROCK64のアナログオーディオ - その5 - アナログオーディオが動かない問題解決(ACODECドライバがなかったから移植)

- ROCK64のアナログオーディオ - 手ごわい44.1kHz系

- ROCK64のアナログオーディオ - RK3328のACODEC

- ROCK64のアナログオーディオ - その6 - 44.1kHzのPCMを再生できない問題解決(GPLLクロック定義のバグを直した)

- ROCK64のアナログオーディオ - その7 - 32kHz → 44.1kHzの順でPCMを再生できない問題解決(fractional dividerの実装を変えた)

- デグレ確認のためASUS Tinker Board購入

- Tinker Boardでは不具合再現せず

- ROCK64でHDMIオーディオを使う

- ROCK64のUSBをデグレさせた

- ROCK64の音がlinux-nextで鳴らなくなった

ROCKPro64シリアル文字化けの話のまとめ。

- ROCKPro64のシリアル文字化け - オシロスコープで解析

- ROCKPro64のシリアル文字化け - 回路図を見る

- ROCKPro64のシリアル文字化け - パッチ投稿

- ROCKPro64のシリアル文字化け - LKMLでの議論

- ROCKPro64のシリアル文字化け - 結論

- ROCKPro64のシリアル文字化け - U-Bootとの比較

- ROCKPro64のシリアル文字化け - 真因発見か?

ROCKPro64オーディオの話のまとめ。

- ROCKPro64のHDMI Audioを有効にする

- ROCKPro64とアナログオーディオ - その1 - linux-nextのドライバ

- ROCKPro64とアナログオーディオ - その2 - Headphone Mixerボリュームのバグ

- ROCKPro64とアナログオーディオ - その3 - DACボリュームの仕様?

- ROCKPro64とオーディオDAC - その1 - I2Cスレーブアドレスの謎

- ROCKPro64とオーディオDAC - その2 - V2.0ボードとV2.1ボード

- ROCKPro64とオーディオDAC - その3 - Linuxのパッチ

- ROCKPro64対ONKYOでSin波の美しさ勝負

- ROCKPro64と音声ビットストリームパススルー出力

- ROCKPro64とSPDIF/HDMIビットストリームパススルー

- ROCKPro64のHDMIから音を出すKconfig設定

- ROCKPro64のI2Sクロックとピン制御

ROCKPro64のその他の話のまとめ。

ROCK 3C/ROCK 5Bの話。

ARM関連の話。

目次: 一覧の一覧

コメント一覧

- コメントはありません。

この記事にコメントする

この記事にコメントする

2020年10月25日

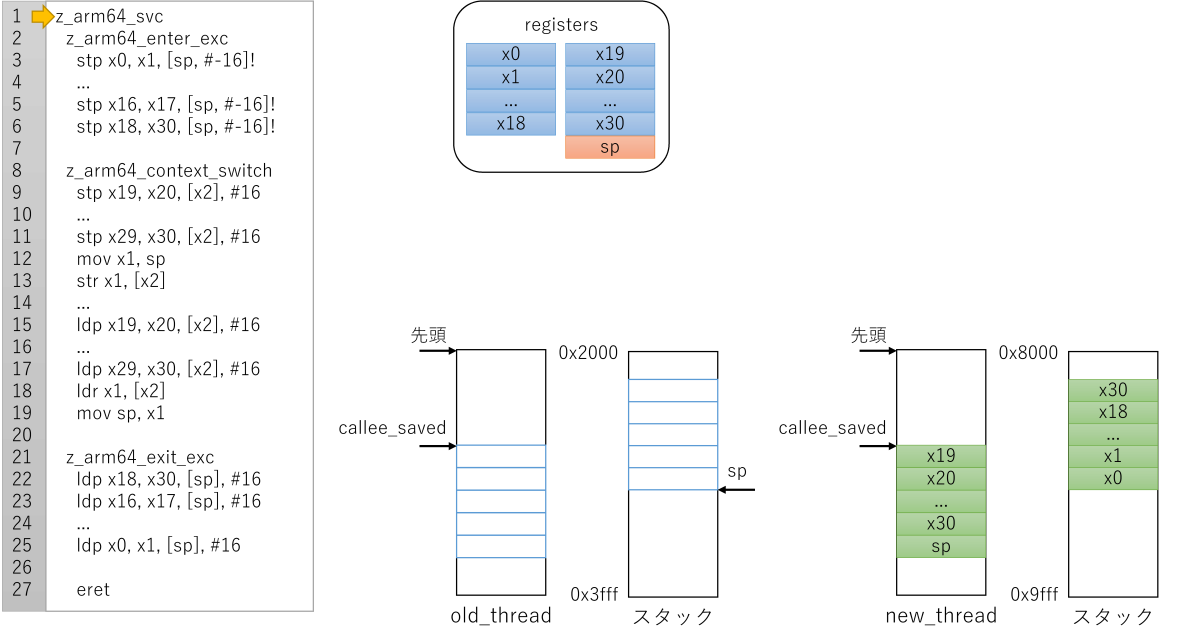

算数の問題

Twitterでこんな問題(リンク)を見かけたので、やってみました。緑色の図形の面積を求めよ、という問題です。

算数で解く=方程式やルートを使わない、という意味だと理解し、図形の合同性だけで解いてみます。

こんな感じで答えは4です。小学生にも解ける問題といえばそうなんでしょうけど、自分が小学生だったころに解けただろうか、と考えるとどうだろうね?

コメント一覧

- コメントはありません。

この記事にコメントする

この記事にコメントする

2020年10月26日

ROCKPro64のI2Sクロックとピン制御

目次: ARM

ROCKPro64でI2S0を無効にすると、なぜか無関係なはずのアナログオーディオ(I2S1)が鳴らなくなる、謎の挙動を示します。原因を調べてみると搭載SoCであるRockchip RK3399の不思議な設計が原因でした。

I2Sは大まかにいうと4種類の信号を使います。

- MCLK

- マスタークロック。DACなどを駆動させるためのクロックです。LRCKの2のべき乗倍を要求されることが多いです。典型的な倍率は128, 256, 384, 512など。

- SCLK

- システムクロック。I2Sデータの1ビットを表すクロックで、LRCKの64倍です。

- LRCK

- LRクロック。I2Sデータフレームのビットが、LチャネルまたはRチャネルのどちらに属するかを示すクロックです。クロック周波数=サンプリング周波数です。

- DATA

- データ。I2S, Left Justify, Right Justifyなどエンコーディングの方法は何通りかあります。

SoC(RK3399)の仕様

RK3399の仕様をみるとMCLKの出力(RK3399のピン名だとI2S_CLK)をI2S0とI2S1で共用しています。普通、MCLKはI2Sに流す信号によって周波数が変わりますから、共用はしません。できる場合もありますが限定的です。

I2Sのハードとしては性能は等価に見えます。ただしSoCのピン設定の仕様を見る限りでは、I2S0は8ch出力まで可能、I2S1は2ch出力のみ可能です。

ボード(ROCKPro64)の仕様

I2S0はRaspberryPi互換ピンヘッダに出力されていますが、MCLKは出力されていない不思議な構成です。MCLKがなくても動くDACはあるのでしょうか……?

I2S1はEverest ES8316というDACに接続され、アナログオーディオIn/Outを実現しています。I2S_CLKはI2S1用、つまりES8316のMCLKに接続されています。

ROCKPro64の仕様としては、I2S0は遊ばせていて、I2S1はアナログオーディオ用に接続している、と考えれば、特に違和感はない構成です。

OS(linux-next)の仕様

Device Treeを見ると、I2S_CLKはI2S0の有効、無効の設定に連動して、出力ピンが制御されるように実装されています。

しかし先ほども言った通りROCKPro64の場合は、I2S_CLKはI2S1のために使われているので、この設定はボードの配線と合っていません。

直し方としては、I2S_CLKをI2S0に連動させる設定(既に存在する)に加えて、I2S_CLKをI2S1に連動させる設定を加えて、ボード側でピン設定を選ぶようにすると直せそうです。Device Tree内のピン設定がやたら増えるのは難点ですが、RK3399の仕様に由来するので仕方ないですね。

コメント一覧

- コメントはありません。

この記事にコメントする

この記事にコメントする

2020年10月31日

FreeRTOSで遊ぼう その5 - FreeRTOSのパッチ投稿の経過

目次: FreeRTOS

FreeRTOSへ送ったPull Requestにレビューコメントが来ました。確かPull Requestは9/14に送ったので1か月半くらい経ってます。FreeRTOSはのんびり屋さんですね。

あまりにも昔なので、送ったことを忘れかけていましたが、せっかくレビューしていただきましたし、内容を思い出しつつ、指摘事項を全て修正して再送しました。

ただ残念ながらFreeRTOSはSMPに対応していないのがわかったときから、あんまり興味がなくなっちゃったんですよね……。

世の中にはSMP対応の派生コード(Xtensa用 by Cadence, Tensilica)、SMPではないマルチコア対応の派生コード(Kendryte用 by Canaan Inc.)もありますが、本家がマルチコア化に全く手を出していないところを見ると、FreeRTOSは質素が売りなんでしょうね。

コメント一覧

- コメントはありません。

この記事にコメントする

この記事にコメントする

こんてんつ

wiki

wiki Linux JM

Linux JM Java API

Java API過去の日記

2002年

2002年 2003年

2003年 2004年

2004年 2005年

2005年 2006年

2006年 2007年

2007年 2008年

2008年 2009年

2009年 2010年

2010年 2011年

2011年 2012年

2012年 2013年

2013年 2014年

2014年 2015年

2015年 2016年

2016年 2017年

2017年 2018年

2018年 2019年

2019年 2020年

2020年 2021年

2021年 2022年

2022年 2023年

2023年 2024年

2024年 2025年

2025年 過去日記について

過去日記についてその他の情報

アクセス統計

アクセス統計 サーバ一覧

サーバ一覧 サイトの情報

サイトの情報