2020年7月18日

北極送り

GitHubが北極にコードを保存する取り組み(私のソースコードが北極送りに? "GitHub" アカウントに謎のラベルが付与されたとの報告が多数 - やじうまの杜 - 窓の杜)をしているそうです。面白いこと考えますよね。

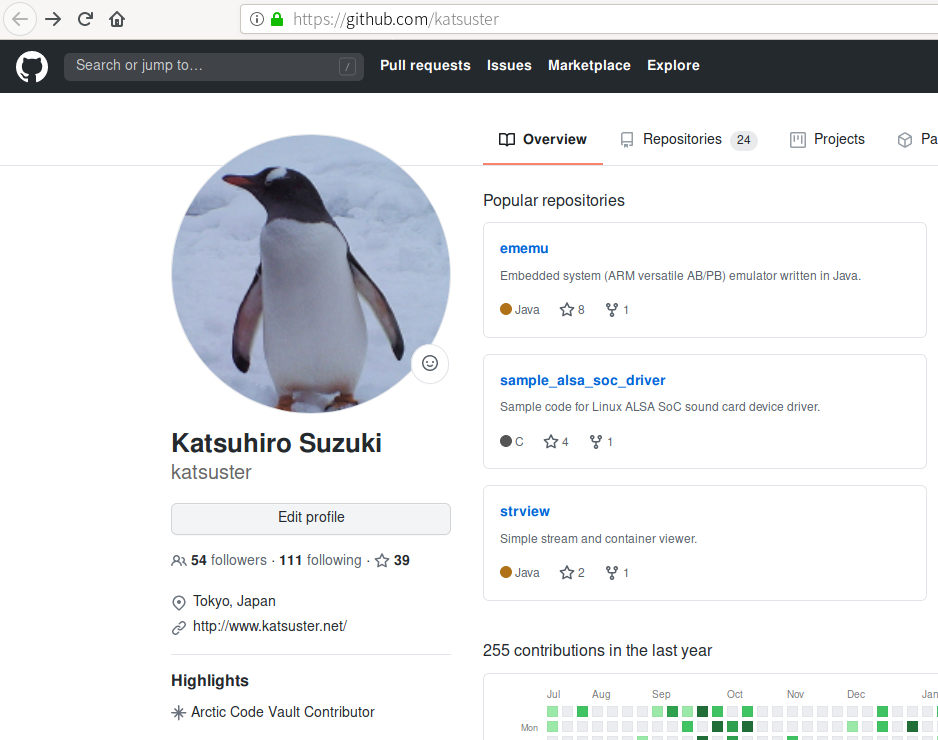

GitHub Arctic Code Vault Contributor

気づいたら自分のGitHubアカウントにもArctic Code Vault Contributorと出ていました。有名なOSSには関わってないし縁がないと思っていましたが、どうやらLinuxにコントリビュートしていたので出てきたっぽいです。いわれてみるとLinuxもGitHubにミラーされてました。

未来人は現代人を理解できるだろうか?

現代人をもってしても1000年前の文字の解読(例: ヒエログリフ、前3200年〜4世紀、19世紀頃に解読された)はとても苦労したこと、解読されていない古代文字がまだまだあることを考えれば、現代文字や文明を遺しても未来人が理解不能で終わってしまう可能性もあるわけです。

少なくとも未来文明は現代文明より遥か上の水準に発展していないと、仮に現代文字や文明を発見できても、真に理解するのは難しいでしょう。

こんなことを考えると、実はCode Vaultの取り組みは「地球の未来は今より進んでいるはず」という信頼や願望が前提になっていることが見て取れます。人類か、それ以外の生命体か、誰の手に渡るかわかりませんが、SF的なロマンがありますよね。

コメント一覧

- コメントはありません。

この記事にコメントする

この記事にコメントする

2020年7月19日

GCCを調べる - その17 - ベクトル四則演算、論理演算の定義

目次: GCC

ベクトルのロード、ストアだけでは自動ベクトル化できるコードが少なすぎるので、他の演算も定義したいと思います。

ベクトル演算の加算、減算、乗算、除算、論理演算(and, or, xor)の定義

;; gcc/config/riscv/riscv.md

(define_attr "vecmode" "unknown,V32SI,V64SI"

(const_string "unknown"))

...

;; Iterator for hardware supported vector modes.

(define_mode_iterator ANYV [(V32SI "TARGET_VECTOR")

(V64SI "TARGET_VECTOR")])

...

;;★★加算

(define_insn "add<mode>3"

[(set (match_operand:ANYV 0 "register_operand" "=v")

(plus:ANYV (match_operand:ANYV 1 "register_operand" " v")

(match_operand:ANYV 2 "arith_operand" " v")))]

"TARGET_VECTOR"

"vadd.vvt%0,%1,%2"

[(set_attr "type" "arith")

(set_attr "vecmode" "<MODE>")])

;;★★減算

(define_insn "sub<mode>3"

[(set (match_operand:ANYV 0 "register_operand" "=v")

(minus:ANYV (match_operand:ANYV 1 "register_operand" " v")

(match_operand:ANYV 2 "arith_operand" " v")))]

"TARGET_VECTOR"

"vsub.vvt%0,%1,%2"

[(set_attr "type" "arith")

(set_attr "vecmode" "<MODE>")])

;;★★乗算

(define_insn "mul<mode>3"

[(set (match_operand:ANYV 0 "register_operand" "=v")

(mult:ANYV (match_operand:ANYV 1 "register_operand" " v")

(match_operand:ANYV 2 "arith_operand" " v")))]

"TARGET_VECTOR"

"vmul.vvt%0,%1,%2"

[(set_attr "type" "arith")

(set_attr "vecmode" "<MODE>")])

;;★★除算

;; This code iterator allows unsigned and signed division to be generated

;; from the same template.

(define_code_iterator any_div [div udiv mod umod])

(define_insn "<optab><mode>3"

[(set (match_operand:ANYV 0 "register_operand" "=v")

(any_div:ANYV (match_operand:ANYV 1 "register_operand" " v")

(match_operand:ANYV 2 "arith_operand" " v")))]

"TARGET_VECTOR"

"v<insn>.vvt%0,%1,%2"

[(set_attr "type" "arith")

(set_attr "vecmode" "<MODE>")])

;;★★論理演算

;; This code iterator allows the three bitwise instructions to be generated

;; from the same template.

(define_code_iterator any_bitwise [and ior xor])

...

(define_insn "<optab><mode>3"

[(set (match_operand:ANYV 0 "register_operand" "=v")

(any_bitwise:ANYV (match_operand:ANYV 1 "register_operand" "%v")

(match_operand:ANYV 2 "arith_operand" " v")))]

"TAREGET_VECTOR"

"v<insn>.vvt%0,%1,%2"

[(set_attr "type" "logical")

(set_attr "vecmode" "<MODE>")])

四則演算、論理演算を使う下記のプログラムを書きます。自動ベクトル化で四則演算のループをベクトル化しても良いですが、ベクトル拡張記法(Vector Extensions (Using the GNU Compiler Collection (GCC)))を使ったほうが狙った演算が出しやすく、テストするときに楽です。

ベクトル四則演算、論理演算のサンプルプログラム

typedef int __v64si __attribute__((__vector_size__(256)));

void test()

{

__v64si v10, v11, v12, v13;0;

__asm__ volatile ("vlw.v %0, %1\n" : "=&v"(v10) : "A"(b[10]));

__asm__ volatile ("vlw.v %0, %1\n" : "=&v"(v11) : "A"(b[20]));

__asm__ volatile ("vlw.v %0, %1\n" : "=&v"(v12) : "A"(b[30]));

__asm__ volatile ("vlw.v %0, %1\n" : "=&v"(v13) : "A"(b[40]));

v10 = v11 + v12;

v11 &= v12 - v13;

v12 |= v13 * v10;

v13 ^= v10 / v11;

__asm__ volatile ("vsw.v %1, %0\n" : "=A"(b[40]) : "v"(v10));

__asm__ volatile ("vsw.v %1, %0\n" : "=A"(b[50]) : "v"(v11));

__asm__ volatile ("vsw.v %1, %0\n" : "=A"(b[60]) : "v"(v12));

__asm__ volatile ("vsw.v %1, %0\n" : "=A"(b[70]) : "v"(v13));

}

ビルド方法は何でも良いですが、最適化レベルをOgにするとアセンブラが見やすいと思います。

ベクトル四則演算、論理演算のサンプルプログラム(逆アセンブル)

$ riscv32-unknown-elf-gcc b.c -nostdlib -g -Og -march=rv32gcv -mabi=ilp32f

$ riscv32-unknown-elf-objdump -dS a.out

...

__asm__ volatile ("vlw.v %0, %1\n" : "=&v"(v13) : "A"(b[40]));

10092: 0a028793 addi a5,t0,160

10096: 1207e207 vlw.v v4,(a5)

v10 = v11 + v12;

1009a: 022081d7 vadd.vv v3,v2,v1

v11 &= v12 - v13;

1009e: 0a120057 vsub.vv v0,v1,v4

100a2: 26010057 vand.vv v0,v0,v2

v12 |= v13 * v10;

100a6: 9641a157 vmul.vv v2,v4,v3

100aa: 2a208157 vor.vv v2,v2,v1

v13 ^= v10 / v11;

100ae: 863020d7 vdiv.vv v1,v3,v0

100b2: 2e1200d7 vxor.vv v1,v1,v4

__asm__ volatile ("vsw.v %1, %0\n" : "=A"(b[40]) : "v"(v10));

100b6: 0207e1a7 vsw.v v3,(a5)

...

うまくいっているようです。良かった良かった。

コメント一覧

- コメントはありません。

この記事にコメントする

この記事にコメントする

2020年7月20日

GCCを調べる - その18 - ベクトルNot演算の定義

目次: GCC

前回(2020年7月19日の日記参照)は四則演算と論理演算(and, or, xor)を定義しました。今回はNot演算を定義します。他の論理演算と異なり、Not演算は2オペランドしか取りませんから、define_insnを別に書く必要があります。

ベクトルNot演算の定義

;; gcc/config/riscv/riscv.md

(define_insn "one_cmpl<mode>2"

[(set (match_operand:ANYV 0 "register_operand" "=v")

(not:ANYV (match_operand:ANYV 1 "register_operand" "%v")))]

"TARGET_VECTOR"

"vnot.vt%0,%1"

[(set_attr "type" "logical")

(set_attr "vecmode" "<MODE>")])

前回同様に、ベクトル拡張記法(Vector Extensions (Using the GNU Compiler Collection (GCC)))を使ってビット毎Notを使うプログラムを書きます。

ベクトルNot演算のサンプルプログラム

typedef int __v64si __attribute__((__vector_size__(256)));

void test()

{

__v64si v10, v11;

static int b[1024 * 1024] = {0};

__asm__ volatile ("vlw.v %0, %1\n" : "=&v"(v10) : "A"(b[10]));

__asm__ volatile ("vlw.v %0, %1\n" : "=&v"(v11) : "A"(b[20]));

v10 = ~v11;

__asm__ volatile ("vsw.v %1, %0\n" : "=A"(b[40]) : "v"(v10));

}

コンパイルするとエラーが発生します。何かお気に召さないようです。

コンパイルエラー

$ riscv32-unknown-elf-gcc b.c -nostdlib -Og -march=rv32gcv -mabi=ilp32f

during RTL pass: reload

dump file: b.c.282r.reload

b.c: In function 'test':

b.c:14:1: internal compiler error: in setup_operand_alternative, at lra.c:814

14 | }

| ^

0xea5c36 setup_operand_alternative

gcc/gcc/lra.c:814

0xea70c2 lra_set_insn_recog_data(rtx_insn*)

gcc/gcc/lra.c:1073

0xea30f9 lra_get_insn_recog_data

gcc/gcc/lra-int.h:488

0xeab0b9 remove_scratches_1

gcc/gcc/lra.c:2058

0xeab4c4 remove_scratches

gcc/gcc/lra.c:2094

0xeac629 lra(_IO_FILE*)

gcc/gcc/lra.c:2396

0xe1a41f do_reload

gcc/gcc/ira.c:5523

0xe1ae5c execute

gcc/gcc/ira.c:5709

コードを見ると最後のオペランドに % を付けるべきではないそうです。確かにdefine_insnを見ると % が要らないのに付いています。

エラーを出している箇所

// gcc/lra.c

/* Setup info about operands in alternatives of LRA DATA of insn. */

static void

setup_operand_alternative (lra_insn_recog_data_t data,

const operand_alternative *op_alt)

{

int i, j, nop, nalt;

int icode = data->icode;

struct lra_static_insn_data *static_data = data->insn_static_data;

static_data->commutative = -1;

nop = static_data->n_operands;

nalt = static_data->n_alternatives;

static_data->operand_alternative = op_alt;

for (i = 0; i < nop; i++)

{

static_data->operand[i].early_clobber_alts = 0;

static_data->operand[i].is_address = false;

if (static_data->operand[i].constraint[0] == '%') //★★% が付いていればcommutative

{

/* We currently only support one commutative pair of operands. */

if (static_data->commutative < 0)

static_data->commutative = i;

else

lra_assert (icode < 0); /* Asm */

/* The last operand should not be marked commutative. */

lra_assert (i != nop - 1); //★★このアサートに引っかかる

}

}

...

素直に応じるとエラーは消えます。

ベクトル演算のNotの定義(修正後)

(define_insn "one_cmpl<mode>2"

[(set (match_operand:ANYV 0 "register_operand" "=v")

(not:ANYV (match_operand:ANYV 1 "register_operand" " v")))] ★★% を消す

"TARGET_VECTOR"

"vnot.vt%0,%1"

[(set_attr "type" "logical")

(set_attr "vecmode" "<MODE>")])

四則演算、論理演算(3オペランド系)と、Not演算(2オペランド系)が揃いました。残りの頻出する演算はビットシフト系かな?

最後のオペランドをcommutativeにできない理由

最後のオペランドをcommutativeにしてはいけない理由は、GCCのConstraintsの説明を見るとわかります。

`%' Declares the instruction to be commutative for this operand and the following operand. This means that the compiler may interchange the two operands if that is the cheapest way to make all operands fit the constraints. GCC can only handle one commutative pair in an asm; if you use more, the compiler may fail. Note that you need not use the modifier if the two alternatives are strictly identical; this would only waste time in the reload pass. The modifier is not operational after register allocation, so the result of define_peephole2 and define_splits performed after reload cannot rely on `%' to make the intended insn match.

難しいことを言っていますが、commutativeは % を付けたオペランドと「次」のオペランドが可換だと宣言することだそうです。最後のオペランドには「次」のオペランドがありませんから、% を付けてはいけません。なるほど。

RISC-Vの場合は論理演算のdefine_insnの2番目のオペランドに % が使われています。

RISC-Vスカラ論理演算の定義

;; gcc/config/riscv/riscv.md

;; This code iterator allows the three bitwise instructions to be generated

;; from the same template.

(define_code_iterator any_bitwise [and ior xor])

...

(define_insn "<optab><mode>3"

[(set (match_operand:X 0 "register_operand" "=r,r")

(any_bitwise:X (match_operand:X 1 "register_operand" "%r,r")

(match_operand:X 2 "arith_operand" " r,I")))]

""

"<insn>%i2t%0,%1,%2"

[(set_attr "type" "logical")

(set_attr "mode" "<MODE>")])

例えばand r1, r2, r3とand r1, r3, r2は結果が同じですから、2番目と3番目のオペランドは入れ替え可能です。3つの論理演算(any_bitwiseはand, or, xorのこと)はいずれも同様に入れ替え可能ですので、このような定義になっています。

コメント一覧

- コメントはありません。

この記事にコメントする

この記事にコメントする

2020年7月21日

ARM SBCリスト2

目次: ROCK64/ROCKPro64

最近はたくさんのARMのシングルボードコンピュータ(SBC)が市販されています。2019年以降のボードも追加してみました。値段は変動するので参考です。

- Amlogic S905X3

- ボードHardkernel ODROID-C4, A55/2.0GHz x 4, 4GB DDR4-2666, 12nm, $50, 2020/04

- Amlogic A311D (S922X + NPU)

- ボードKhadas KVIM3-P-002, A73/2.2GHz x 4, A53/1.8GHz x 2, 4GB LPDDR4-????, 12nm, $160, 2019/06

- Amlogic S912

- ボードKhadas KVIM2-M-002, A53/1.5GHz x 8, 3GB DDR4-????, 28nm, $170, 2017/08

- Broadcom BCM2711

- ボードRaspberry Pi 4 Model B, A72/1.5GHz x 4, 8GB LPDDR4, 28nm, $75, 2019/11

- HiSilicon Kirin 970

- ボード96boards HiKey 970, A73/2.36GHz x 4, A53/1.8GHz x 4, 6GB LPDDR4-1866, 10nm, $299, 2018/??

- MediaTek Helio X20

- ボード96boards MediaTek X20, A72/2.1GHz x 2, A53/1.85GHz x 4, A53/1.4GHz x 4, 2GB LPDDR3-????, 20nm, $199, 2017/??

- NVIDIA Xavier AGX

- ボードNVIDIA Jetson Xavier AGX, Carmel/2.26GHz x 8, 8MB L2, 4MB L3, 32GB LPDDR4-2133, 12nm, $700, 2020/??

- NVIDIA Xavier NX

- ボードNVIDIA Jetson Xavier NX, Carmel/1.4GHz x 6, 6MB L2, 4MB L3, 8GB LPDDR4-1600, 12nm, $400, 2020/??

- Rockchip RK3399

- ボードFriendlyARM NanoPC-T4, A72/2GHz x 2, A53/1.5GHz x 4, 4GB LPDDR3-1866, 28nm, $109, 2018/??

- Samsung S5P6818

- ボードFriendlyARM NanoPC-T3 Plus, A53/1.4GHz x 8, 2GB DDR3, $75, 2018/??

古い世代のSoCを採用したボード達です。

- AllWinner H6

- ボードPINE64 PINE H64, A53 x 4, 2GB LPDDR3-1600, 28nm, $36

- AllWinner H5

- ボードFriendlyARM NanoPi NEO2, A53/1.5GHz x 4, 1GB DDR3, 40nm, $20

- Amlogic S905

- ボードHardkernel ODROID-C2, A53/1.5GHz x 4, 2GB DDR3-1866? (912MHz), 28nm, $39

- Broadcom BCM2837B

- ボードRaspberry Pi 3 Model B, A53/1.2GHz x 4, 1GB LPDDR2, 28nm, $35

- HiSilicon Kirin 960

- ボードHiKey 960, A72 x 4, A53 x 4, 3GB LPDDR4, 16nm FinFET, $239

- NVIDIA Tegra X2 (Parker)

- ボードJetson TX2, Denver/2GHz x 2, A57/2GHz x 4, 8GB LPDDR4, 16nm, $600

- NVIDIA Tegra X1

- ボードJetson TX1, A57/1.9GHz x 4, 4GB LPDDR4, 20nm, $500

- Rockchip RK3328

- ボードPINE64 ROCK64, A53/1.4GHz x 4, 4GB LPDDR3-1866, 28nm, $24.95 (1GB) $34.95 (2GB) $44.95 (4GB)

以前(2019年5月15日の日記参照)載せた情報も含んでいます。

コメント一覧

- コメントはありません。

この記事にコメントする

この記事にコメントする

| < | 2020 | > | ||||

| << | < | 07 | > | >> | ||

| 日 | 月 | 火 | 水 | 木 | 金 | 土 |

| - | - | - | 1 | 2 | 3 | 4 |

| 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| 12 | 13 | 14 | 15 | 16 | 17 | 18 |

| 19 | 20 | 21 | 22 | 23 | 24 | 25 |

| 26 | 27 | 28 | 29 | 30 | 31 | - |

こんてんつ

wiki

wiki Linux JM

Linux JM Java API

Java API過去の日記

2002年

2002年 2003年

2003年 2004年

2004年 2005年

2005年 2006年

2006年 2007年

2007年 2008年

2008年 2009年

2009年 2010年

2010年 2011年

2011年 2012年

2012年 2013年

2013年 2014年

2014年 2015年

2015年 2016年

2016年 2017年

2017年 2018年

2018年 2019年

2019年 2020年

2020年 2021年

2021年 2022年

2022年 2023年

2023年 2024年

2024年 過去日記について

過去日記についてその他の情報

アクセス統計

アクセス統計 サーバ一覧

サーバ一覧 サイトの情報

サイトの情報合計:

本日:

管理者: Katsuhiro Suzuki(katsuhiro( a t )katsuster.net)

This is Simple Diary 1.0

Copyright(C) Katsuhiro Suzuki 2006-2023.

Powered by PHP 8.2.15.

using GD bundled (2.1.0 compatible)(png support.)