2019年7月18日

C言語とCPUアーキテクチャと除算命令

目次: C言語とlibc

今まであまりCPUアーキテクチャの違いを感じたことはありませんが、除算命令を触っていたところ、アーキテクチャによってかなり動きが違っていて面白かったので、メモしておきます。

プログラムは下記のとおりです。

-1による除算

#include <stdio.h>

#include <limits.h>

void f(int a, int b)

{

printf("mul:%08x * %08x = %08x\n", a, b, a * b);

printf("div:%08x / %08 = %08x\n", a, b, a / b);

}

int main(int argc, char *argv[])

{

f(INT_MAX, -1);

f(INT_MIN + 1, -1);

f(INT_MIN, -1); //乗算、除算の動作は未定義

f(INT_MAX, 0); //除算の動作は未定義

}

初めに断っておくと、コメントを打った箇所については、C言語上の仕様上、動作が未定義です。つまり、どんなことでも起こり得ます。不定な結果が返ることもあるし、プログラムが停止することだってあります。

未定義動作も色々

このプログラムをx86 (x86_64, Ryzen 7 2700), ARM (AArch64, Cortex A53), RISC-V (RV64GC, SiFive FU540) のLinux上でそれぞれ実行してみます。

各アーキテクチャでの実行結果

#### x86_64 ####

mul:7fffffff * ffffffff = 80000001

div:7fffffff / ffffffff = 80000001

mul:80000001 * ffffffff = 7fffffff

div:80000001 / ffffffff = 7fffffff

mul:80000000 * ffffffff = 80000000

Floating point exception

#### AArch64 ####

mul:7fffffff * ffffffff = 80000001

div:7fffffff / ffffffff = 80000001

mul:80000001 * ffffffff = 7fffffff

div:80000001 / ffffffff = 7fffffff

mul:80000000 * ffffffff = 80000000

div:80000000 / ffffffff = 80000000

mul:7fffffff * 00000000 = 00000000

div:7fffffff / 00000000 = 00000000

#### RV64GC ####

mul:7fffffff * ffffffff = 80000001

div:7fffffff / ffffffff = 80000001

mul:80000001 * ffffffff = 7fffffff

div:80000001 / ffffffff = 7fffffff

mul:80000000 * ffffffff = 80000000

div:80000000 / ffffffff = 80000000

mul:7fffffff * 00000000 = 00000000

div:7fffffff / 00000000 = ffffffff

当然ながら、動作が定義されている演算は、どのアーキテクチャでも同じ結果です。当たり前ですね。

- INT_MAX * (-1) = INT_MIN + 1

- INT_MAX / (-1) = INT_MIN + 1

- (INT_MIN + 1) * (-1) = INT_MAX

- (INT_MIN + 1) / (-1) = INT_MAX

- INT_MAX * 0 = 0

一方で動作が未定義の演算は、かなり挙動が変わります。

- INT_MIN * (-1) = INT_MIN

- INT_MIN / (-1) = クラッシュ (x86_64), INT_MIN (AArch64, RV64GC)

- INT_MAX / 0 = クラッシュ (x86_64), 0 (AArch64), -1 (RV64GC)

個性が出ますね。

x86の除算命令の奇妙な仕様

先ほどの例でx86上でINT_MIN / (-1) の除算がクラッシュする原因はidiv命令の仕様です。

Intelの命令仕様書(Intel Architectures Software Developer Manual: Vol 2)のIDIV - Signed Divideのページを見ると、保護モード例外 #DEが発生する条件として、

- ソース・オペランド(除数)が0である場合

- デスティネーションに対して符号付きの結果(商)が大きすぎる場合

この2条件が挙げられています。INT_MIN / (-1) は結果が32bitで表現できないため、後者に引っ掛かるわけです。

異常な演算に対して例外を発生させる設計思想なら分かりますが、乗算命令は異常な結果でも素通しなのに、除算命令は異常な結果だと例外発生します。片手落ちの不思議な仕様です。変なの……。

コメント一覧

- hdkさん(2019/07/20 00:23)

x86の除算例外は8086/8088の頃からありました。乗算については、8ビット同士を掛けて16ビットを出すか、16ビット同士を掛けて32ビットを出すかしかなかったので、異常な結果というのがそもそもなかったんですよね。(下位ビットだけ使うのはCコンパイラーの勝手なので。) 今はIMUL命令のオペランドが増えて同一ビット幅の答えを返す命令もありますが、例外がないのは名残か、あるいは、同じく例外がないシフトと足し算の命令の代わりに使われることを意図したかでしょうか。想像ですが。 - すずきさん(2019/07/20 10:56)

MUL については、結果が倍のビット幅になっていたからという理屈もわかるんですが、加算、減算はオーバーフローしたらOFをセットするだけなのに、「除算だけ」オーバーフローで例外を発生させるのは、変な仕様です。。。 - すずきさん(2019/07/20 11:02)

OFをセットして例外を出したければINTOでオーバーフロー例外(#OF)を発生させるのがx86の仕様に思えるのですが、除算だけ特別というかわざわざ除算例外(#DE)なんて用意しているのも不思議です……。 - hdkさん(2019/07/24 07:25)

加算減算は符号のありなしどちらも命令が同じですから、オーバーフローで即例外ってわけにはいかないですね。まぁ確かに除算も不正な解を出してフラグを立てる実装もありそうですが、除算回路が止まっちゃうのかなーという気も... ちなみにAAM命令でも0を指定すれば#DE発生させられます。 - すずきさん(2019/07/24 22:22)

AAM(ASCII Adjust AX After Multiply)って使ったことないですが、乗算系の命令でも #DE 発生するんですね。

一貫性が無い感じが x86 らしいといえばらしいです。。。 - hdkさん(2019/07/25 00:02)

あっ、AAMはマニュアルのオペレーションを見ていただくとわかりますが中身は除算命令ですので、乗算系とは言えない気がします。DIV命令と違って8ビットを8ビットで割って8ビットの商と余りを出すので(全部符号なし整数)、0除算以外に例外が発生する条件はありません。

この記事にコメントする

この記事にコメントする

2019年7月21日

RISC-Vの命令

目次: RISC-V

最近、何かと関わっているRISC-Vの理解のため、エミュレータを書いてみています。先日購入したHiFive Unleashed(2019年5月26日の日記参照)の1st ROMと2nd ROMを拝借して、Linuxがブートする辺りまで作るのが当面の目標です。

スクラッチから作ると辛いので、ARMv5のエミュレータememu(GitHubへのリンク)をベースにして改造して作っています。まがりなりにもARMv5が動いているんだから、RISC-Vも楽勝だろうと思いきや、世の中そんなに甘くありませんでした。

最初にコケたのはUnalignedな命令ロードです。RISC-VのC拡張をサポートする場合32bit境界ではないアドレスから、32bit命令をロードする場合があります。ARMv5ではUnalignedアクセス例外が発生します。

RISC-Vの命令エンコード

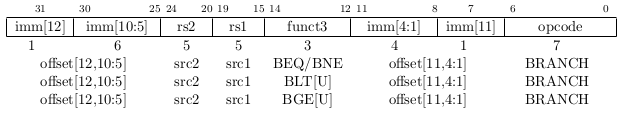

まだ完成していないので、現時点での感想ですが、RISC-Vの命令エンコードは比較的わかりやすい気がします。ただ、ブランチ命令のオフセットは、下記のような並びになっていて、不思議な配置です。

今まで見た中で一番見づらいものは、C拡張命令のバイナリです、これは異様に見づらいです。しかしC拡張の目的(命令長を削るため16bit長に無理して詰めている)からすると、仕方ないでしょうね。

コメント一覧

- コメントはありません。

この記事にコメントする

この記事にコメントする

| < | 2019 | > | ||||

| << | < | 07 | > | >> | ||

| 日 | 月 | 火 | 水 | 木 | 金 | 土 |

| - | 1 | 2 | 3 | 4 | 5 | 6 |

| 7 | 8 | 9 | 10 | 11 | 12 | 13 |

| 14 | 15 | 16 | 17 | 18 | 19 | 20 |

| 21 | 22 | 23 | 24 | 25 | 26 | 27 |

| 28 | 29 | 30 | 31 | - | - | - |

こんてんつ

wiki

wiki Linux JM

Linux JM Java API

Java API過去の日記

2002年

2002年 2003年

2003年 2004年

2004年 2005年

2005年 2006年

2006年 2007年

2007年 2008年

2008年 2009年

2009年 2010年

2010年 2011年

2011年 2012年

2012年 2013年

2013年 2014年

2014年 2015年

2015年 2016年

2016年 2017年

2017年 2018年

2018年 2019年

2019年 2020年

2020年 2021年

2021年 2022年

2022年 2023年

2023年 2024年

2024年 過去日記について

過去日記についてその他の情報

アクセス統計

アクセス統計 サーバ一覧

サーバ一覧 サイトの情報

サイトの情報合計:

本日:

管理者: Katsuhiro Suzuki(katsuhiro( a t )katsuster.net)

This is Simple Diary 1.0

Copyright(C) Katsuhiro Suzuki 2006-2023.

Powered by PHP 8.2.15.

using GD bundled (2.1.0 compatible)(png support.)